This post is also available in: 英語 簡体中国語

世界最高水準のPZTスパッタ膜を安定成膜できます。(CMOS上成膜対応:PZT成膜温度 <500℃)

マルチチャンバー搭載で、PZT full stack(上下電極+PZT)を一貫成膜可能です。

課題

・500℃以下の低温プロセス

圧電MEMSをCMOSへ搭載するには500℃以下の低温プロセスが必要だが、PZTの結晶化にはスパッタリング法で600℃必要

・高い圧電性能と信頼性の両立

・量産化に向けた高スループットと高い再現性

解決策

・バッファ層の活用

バッファ層を活用し、500℃以下でのPZTの結晶化を実現

・PZTスパッタ向けのハードウェア

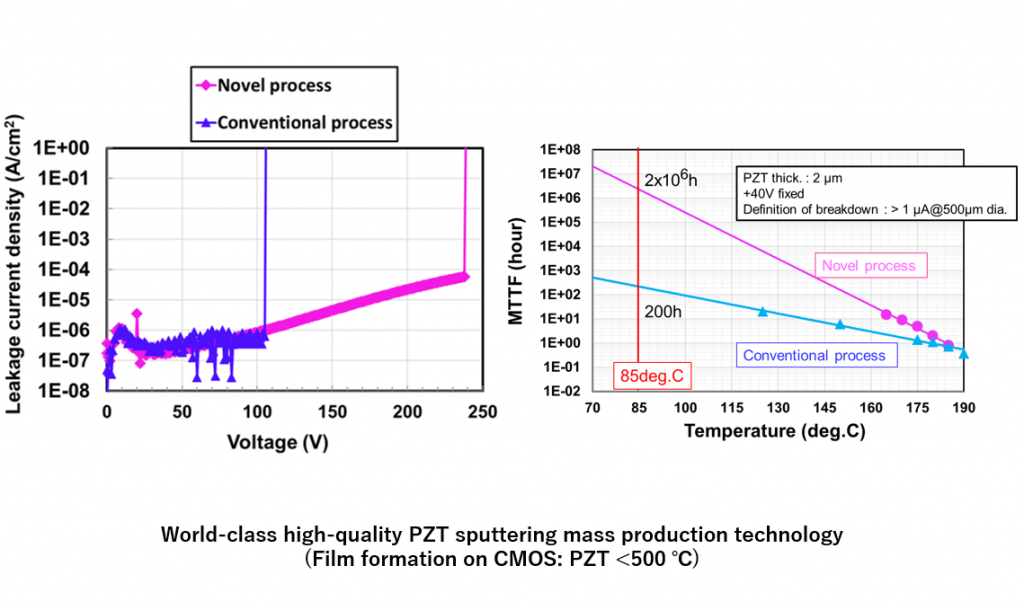

500℃以下の低温プロセスでありながら優れた圧電性能と高信頼性を両立

・同一装置内でPZT構成を実現

クラスター式スパッタリング装置のため各積層構造を同一装置内で成膜

Specification of ULVAC PZT supttering

| Item | Specification | Advantage |

| Deposition temperature | <500 deg.C | On CMOS |

| Wafer size | 8 inch | Mass Production |

| Deposition rate | 4 μm/h | |

| Thickness uniformity | ±3.0% | |

| Pb content uniformity | ±0.6% | |

| Stress uniformity | Δ64MPa (Max-Min) | |

| Crystalline orientation | c-axis | High Performance |

| Morphorogy | Ra : 3.2 nm | |

| Piezoelectric coefficient :|e31| | ~ 15.5 C/m2 | |

| Breakdown voltage | ~ 200V (@2.0μm) | |

| TDDB(45V, 80 deg.C) | >2x 106 hours | |

|

||