This post is also available in: 日语 英语

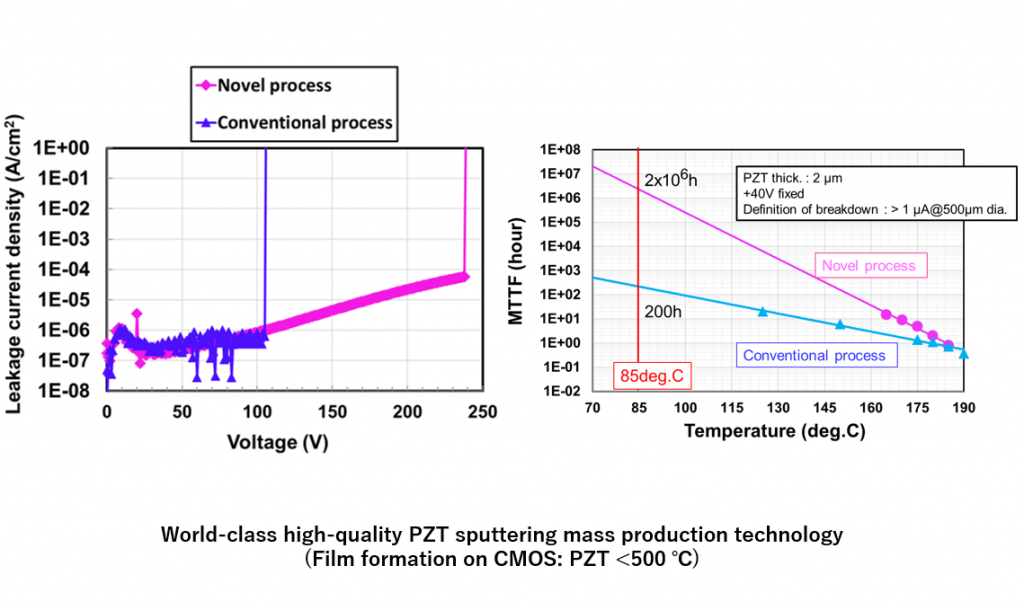

可以稳定形成世界最高水平的PZT溅射膜。(MEMS on CMOS成膜对应:PZT成膜温度 <500℃)

搭载多腔室,可以实现PZT full stack(上下电极+PZT)一致成膜。

Challenge

・500℃以下低温工艺

MEMS on CMOS制作时,需要500℃以下的低温工艺,但是要使PZT结晶化,需要通过溅射的方法必须要达到600℃

・高压电性能和高可靠性并存

・面向量产化的高产能和高再现性

解決方案

・Buffer Layer的活用

活用Buffer Layer、在 500°C以下实现 PZT 结晶

・面向PZT溅射的硬件

在500℃以下的低温工艺中,兼具优秀的压电性能和高可靠性

・在同一设备中实现 PZT 配置

由于是cluster式溅射设备,因此在同一设备中可对各膜层结构进行成膜

Specification of ULVAC PZT supttering

| Item | Specification | Advantage |

| Deposition temperature | <500 deg.C | On CMOS |

| Wafer size | 8 inch | Mass Production |

| Deposition rate | 4 μm/h | |

| Thickness uniformity | ±3.0% | |

| Pb content uniformity | ±0.6% | |

| Stress uniformity | Δ64MPa (Max-Min) | |

| Crystalline orientation | c-axis | High Performance |

| Morphorogy | Ra : 3.2 nm | |

| Piezoelectric coefficient :|e31| | ~ 15.5 C/m2 | |

| Breakdown voltage | ~ 200V (@2.0μm) | |

| TDDB(45V, 80 deg.C) | >2x 106 hours | |

|

||