This post is also available in:

英語 簡体中国語

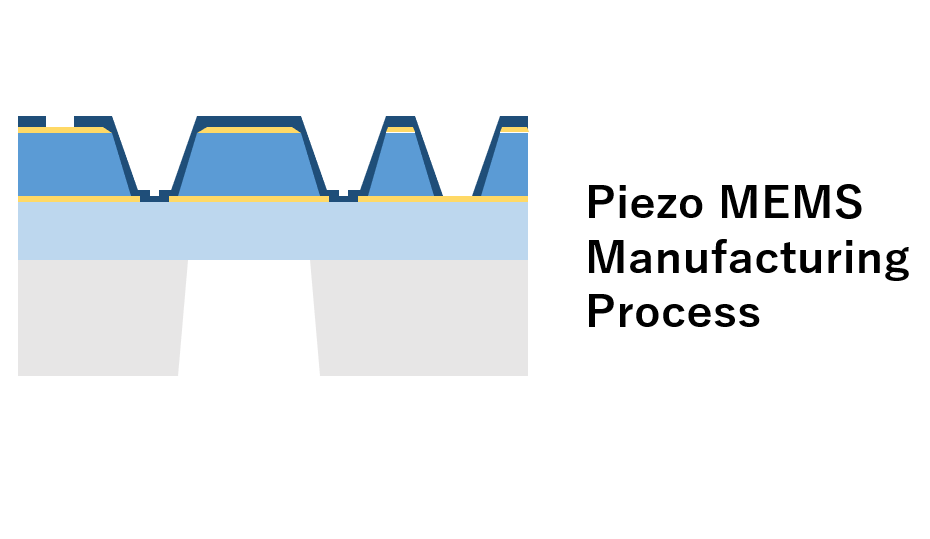

近年MEMSデバイス技術はますます進化し、各種センサー、アクチュエータに不可欠な存在になっています。 その中でもMEMSの小型化、高性能化への貢献が期待される圧電材料の活用が期待されています。圧電材料の中でも優れた圧電特性を有するPZTを例に圧電MEMSの製造プロセスと必要となる技術を紹介します。

圧電MEMSのプロセスフロー

|

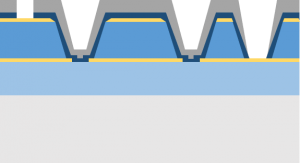

1. 圧電素子の形成

数μmの強誘電体を貴金属電極で挟むことで圧電素子が形成されます。

ULVACが提供するスパッタ装置は世界最高水準のPZTスパッタ膜を安定成膜できます。(CMOS上成膜対応:PZT成膜温度 <500℃) マルチチャンバー搭載で、PZT full stack(上下電極+PZT)を一貫成膜可能です。

PZT低温スパッタリングのプロセス紹介

マルチチャンバ型スパッタリング装置紹介 |

|

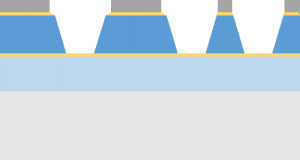

2. 上部電極Pt/PZTエッチング

レジストマスクを塗布します。

ドライエッチングにより上部電極およびPZTをエッチングし素子分離します。下部電極であるPtとの高い選択性を持つPt/PZTエッチングプロセスを提供します。(選択比例:PZT/Pt>5@8inch, >10@6inch)

PZTエッチングのプロセス紹介

ドライエッチング装置紹介 |

|

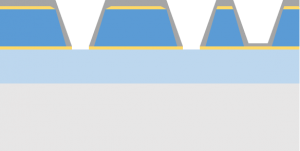

3. 下部電極Ptエッチング

レジストマスクを塗布します。

ドライエッチングにより下部電極を素子分離します。下部電極の下の材料を削り過ぎないため、高い均一性と精密な終点検出を実現しています。(分布<3%@8inch)

PZTエッチングのプロセス紹介

ドライエッチング装置紹介 |

|

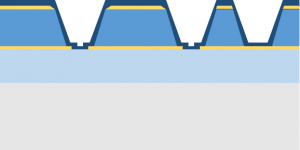

4. 保護膜の形成

CVDによりSiO2の保護膜を成膜します。 |

|

5. 電極部分の引き出し

電極部分を引き出すためにSiO2をエッチングします。 |

|

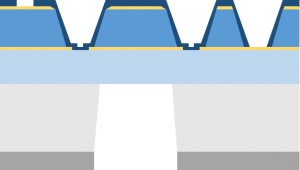

6. 中空構造の形成

裏面のシリコンをドライエッチングし、可動部分を形成します。 |

本プロセスに関するお問い合わせはこちら