This post is also available in: 英語

1.はじめに

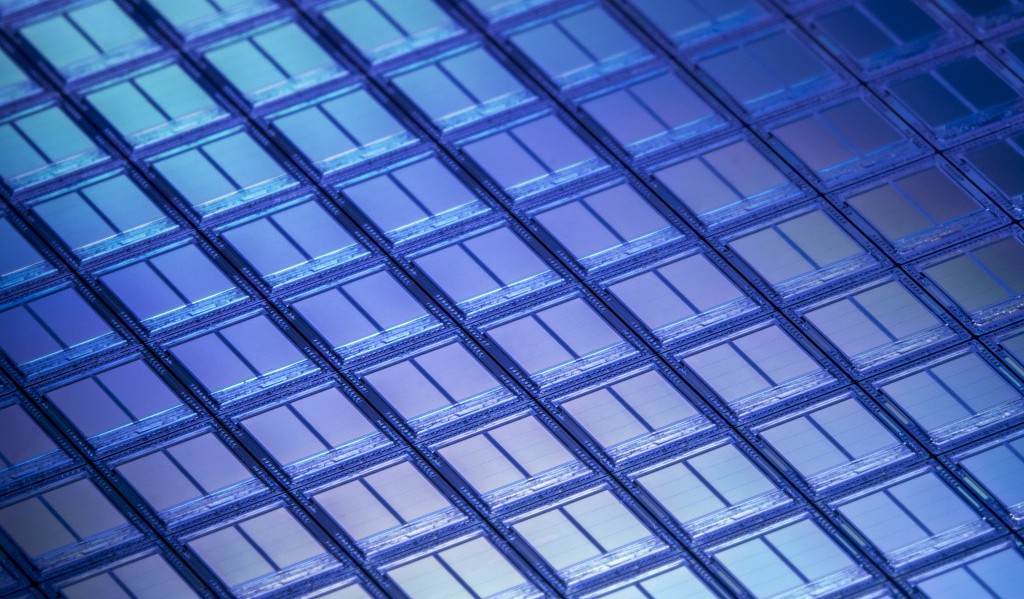

近年,スマートフォン,タブレットPC に代表されるモバイル端末の急速な普及によりIC チップの薄化・小型化が進んでいる.これに対応し,IC パッケージ基板も高密度・薄型化ニーズが高まっており,基板を構成する支持体であるコア層の薄型化も進んでいる1).一方,ハイエンドサーバ等では,チップサイズが大きく,それによって基板も大型である必要がある.この様にモバイルアプリからサーバアプリと広き分野にわたり高密度実装化トレンドニーズに対応すべく,PCB(Print Circuit Board)基板のビルドアップ配線形成において,半導体微細化加工技術の導入検討が始まっている.PCB 基板は510 mm×510 mm あるいはそれ以上の四角基板(パネル)で,反りや耐熱性および機械的特性理解とこれら多様なパネルのハンドリングは,従来のシリコンウエーハ工程とは異なる特有の課題が存在する2).本寄稿では,当社が世界に先駆けてリリースを始めたパネルレベル実装ソリューションの最新の状況について紹介する.

(※この記事は、2017年2月発行のテクニカルジャーナルMo.80に掲載されたもので、内容は取材時のものです。)

2.パネルレベルビルドアップ工程のドライ化

2.1 プラズマエッチング技術を用いたドライデスミア応用

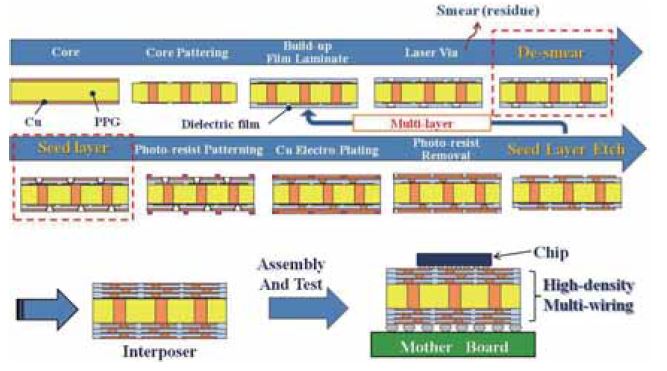

Figure 1 はPCBインターポーザー製造(ビルドアップ)工程及を示す.各絶縁膜層を上下で繋ぐVia の形成はCO2 レーザードリルが用いられる.Via 形成後,Via 底には「スミア:Smear」と呼ぶ残渣が残る.ビルドアップ膜の材質はエポキシ樹脂と,「シリカフィラー」と呼ぶSiO2 粒子の混載物から成り,一般には「ガラスエポキシ膜」と呼ぶ.スミアもエポキシ樹脂とシリカフィラーから成る.スミアが残ったまま次工程に進んだ場合,Cu との密着性低下や配線の抵抗成分の増加等,配線信頼性低下に繋がる.従ってスミア除去,即ち「デスミア(Desmear)」工程が不可欠となる.現世代はウエットで除去できるが,Via 径50 μm 以下の小径化トレンドにおいて,様々な課題が見え始めている.例えば1.異なる膜質に対して同ウエット処理条件の転用/調整が困難,2.微細Via の寸法変換精度の制御限界(膨潤課題),3.Via 側壁の平滑性制御の限界,4.高アスペクト比(>2)対応の不得手,といった点が主に挙げられる.

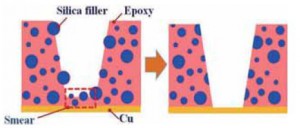

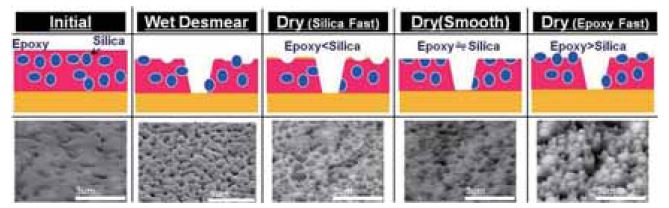

Figure 2はウエットデスミアからドライデスミア展開の必要性を示す3).図からわかるように,ドライエッチングを用いた場合,デスミア除去時にVia 側壁のシリカフィラーの凹凸も同時にスムージングすることができる.本寄稿に用いたエッチング装置はCCP-RIE(Capacitive Coupling Plasma-Reactive Ion Etch)方式を用いた.また,ガラスエポキシ膜は,BF(Ajinomoto Build-up Film)を主に用いた.

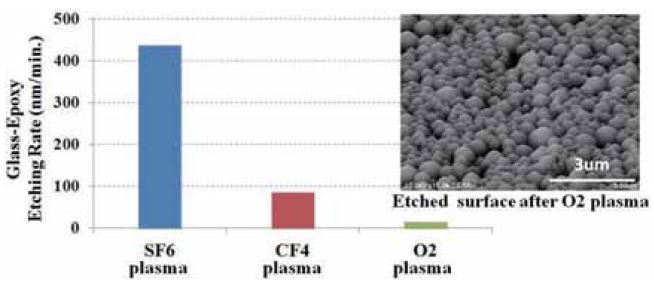

Figure 3 はSF6,CF4,O2 の各ガスを用いてガラスエポキシ表面をエッチングした時のガラスエポキシ膜のエッチングレートを示す.エッチングレートはSF6 が最も早く,O2 は最も遅い.これはシリカフィラーが酸素だけではエッチングしないことに起因する.Figure 4はこれらガスの混合比率を変えた時のガラスエポキシ膜

のエッチング表面荒れのトレンドを示す.結果,エポキシ樹脂とシリカフィラーのエッチングレートが同じくらいを得るガス混合比条件を適用することでエッチング表

面の平滑性が制御できることが判明した.ウエットデスミアの場合の表面を比較に示すが,ウエット処理の方が明らかに表面荒れが大きいことがわかる.以上の結果,プラズマエッチングはウエットプロセスに比べ,各プラズマ条件(ガス比,その他パラメータ)を材質や型式毎に最適化(調整)することができる利点を実証する結果と考察できる.

記事の続きはアルバックテクニカルジャーナルにユーザ登録するとご覧いただけます。

https://www.ulvac.co.jp/r_d/technical_journal/user_registration/

1) 中村吉宏,加藤木茂樹;「半導体実装基板の歩みと今後の技術動向」日立化成テクニカルレポート(2013)No.55,25.

2) 岩澤綾子,佐藤茂樹,中村禎志,越後文雄;「線膨張材料を用いた半導体パッケージ基板の開発」第20 回マイクロエレクトロニクスシンポジウム,立命館大学(2010)235.

3) Yasuhiro Morikawa, Muneyuki Sato, Yosuke Sakao,Tetsushi Fujinaga, Noriaki Tani, Kazuya Saito;“Fabrication of Ultra-Fine Vias in Low CTE Build-up Films Using a Novel Dry Etching Technology” IEEE Electronic Components & Technology Conference,San Diego, CA(2015)1494.