共同開発プロジェクト「Lab-in-Fab(ラボ・イン・ファブ)」が、新たなフェーズに移行したことをお知らせします。今後も引き続きこの取り組みに参加し、技術の進展と社会への応用に貢献してまいります。

「Lab-in-Fab」とは?

Lab-in-Fabは、世界的な半導体企業であるSTマイクロエレクトロニクスがシンガポール・アンモーキオ・キャンパスを拠点に展開する共同研究プロジェクトです。圧電MEMSデバイスの研究開発から製造までを一貫して行える体制が整っており、大学、スタートアップ、中小企業、多国籍企業などが連携しながら、技術の商業化や人材育成を進めています。

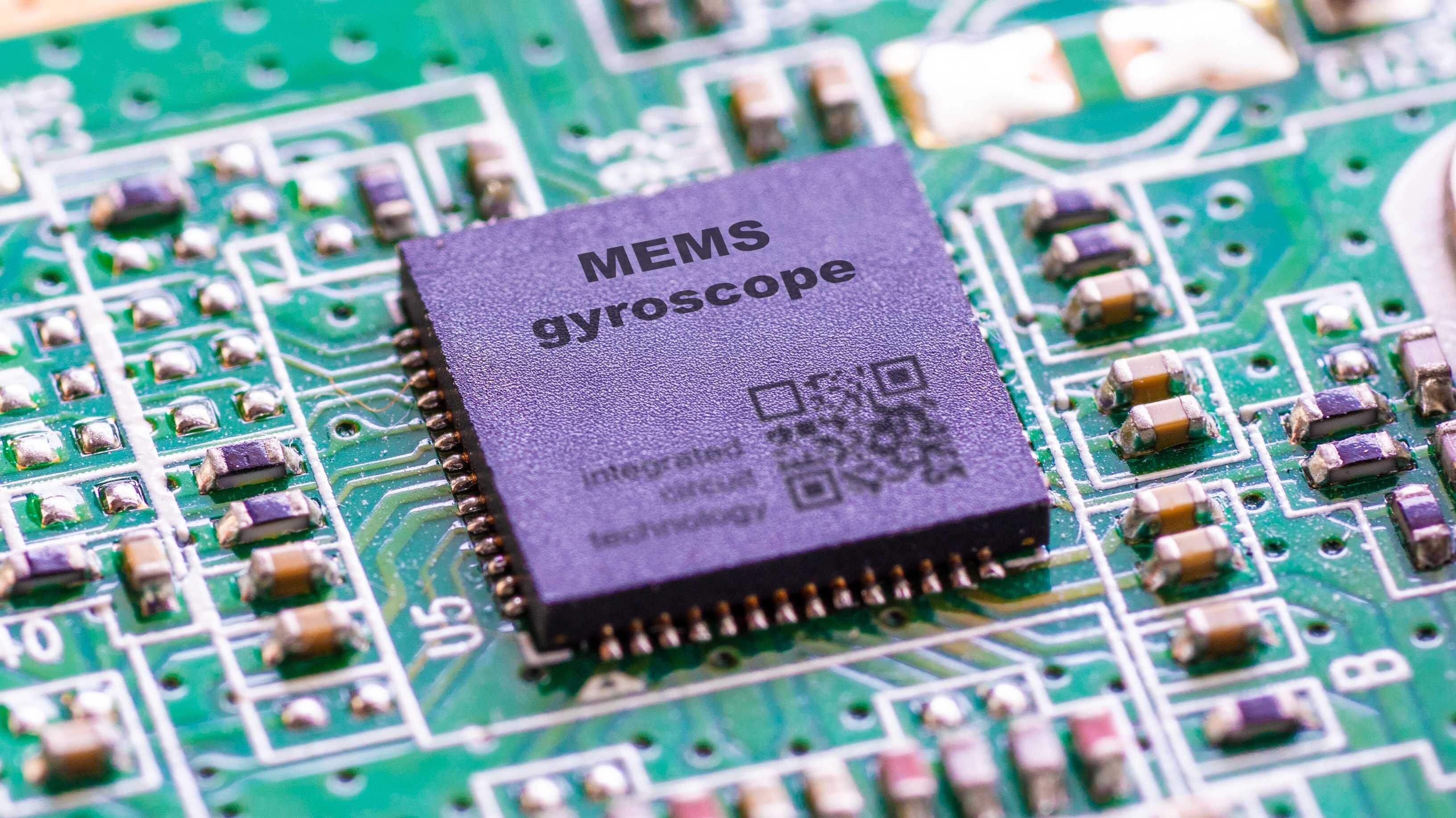

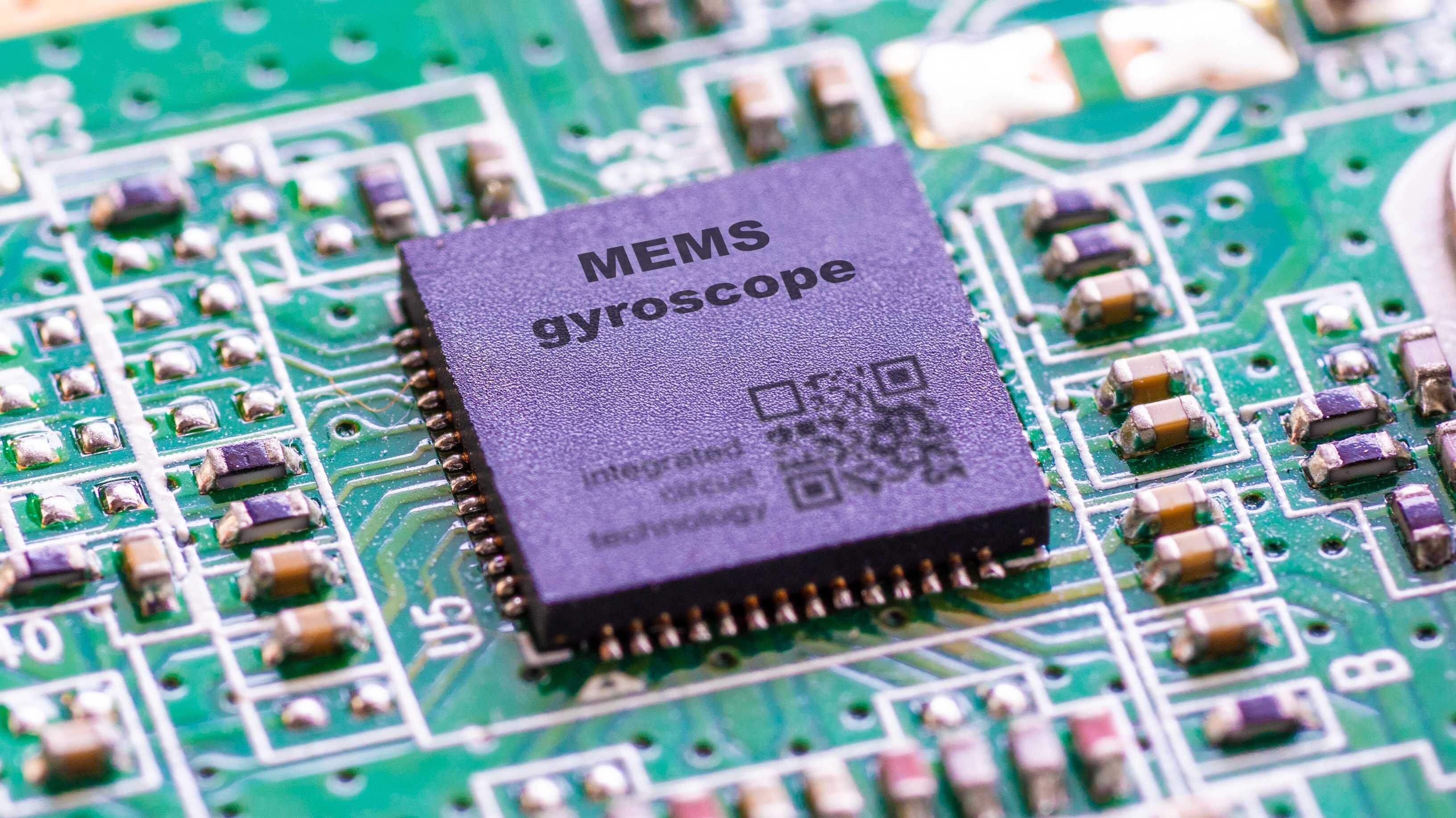

圧電MEMS(Piezoelectric MEMS)は、微細な圧力や振動を電気信号に変換する次世代デバイスで、ウェアラブル機器、音声インターフェース、医療モニタ、ロボティクス、通信機器など、さまざまな分野での小型化・高性能化を支える重要な技術です。

アルバックの役割とこれまでの取り組み

アルバックは装置メーカーとして、圧電MEMSの成膜・加工技術を提供し、技術の実用化を支えています。プロジェクト初期フェーズ(2020年)では、STマイクロエレクトロニクスおよびシンガポール科学技術研究庁(A*STAR)傘下のInstitute of Microelectronicsと連携し、環境負荷の低減を目指して鉛の使用量を抑えたPZT(チタン酸ジルコン酸鉛)薄膜の製造技術を開発しました。

新フェーズでは、A*STARのInstitute of Materials Research and Engineeringやシンガポール国立大学が新たに加わり、鉛フリーの環境配慮型材料の研究開発や、小型・低コストのセンサー、アクチュエーターの実現に向けた取り組みが進められています。

今後もアルバックは、装置技術の革新とグローバルな連携を通じて、次世代のものづくりの実現に向けて邁進してまいります。

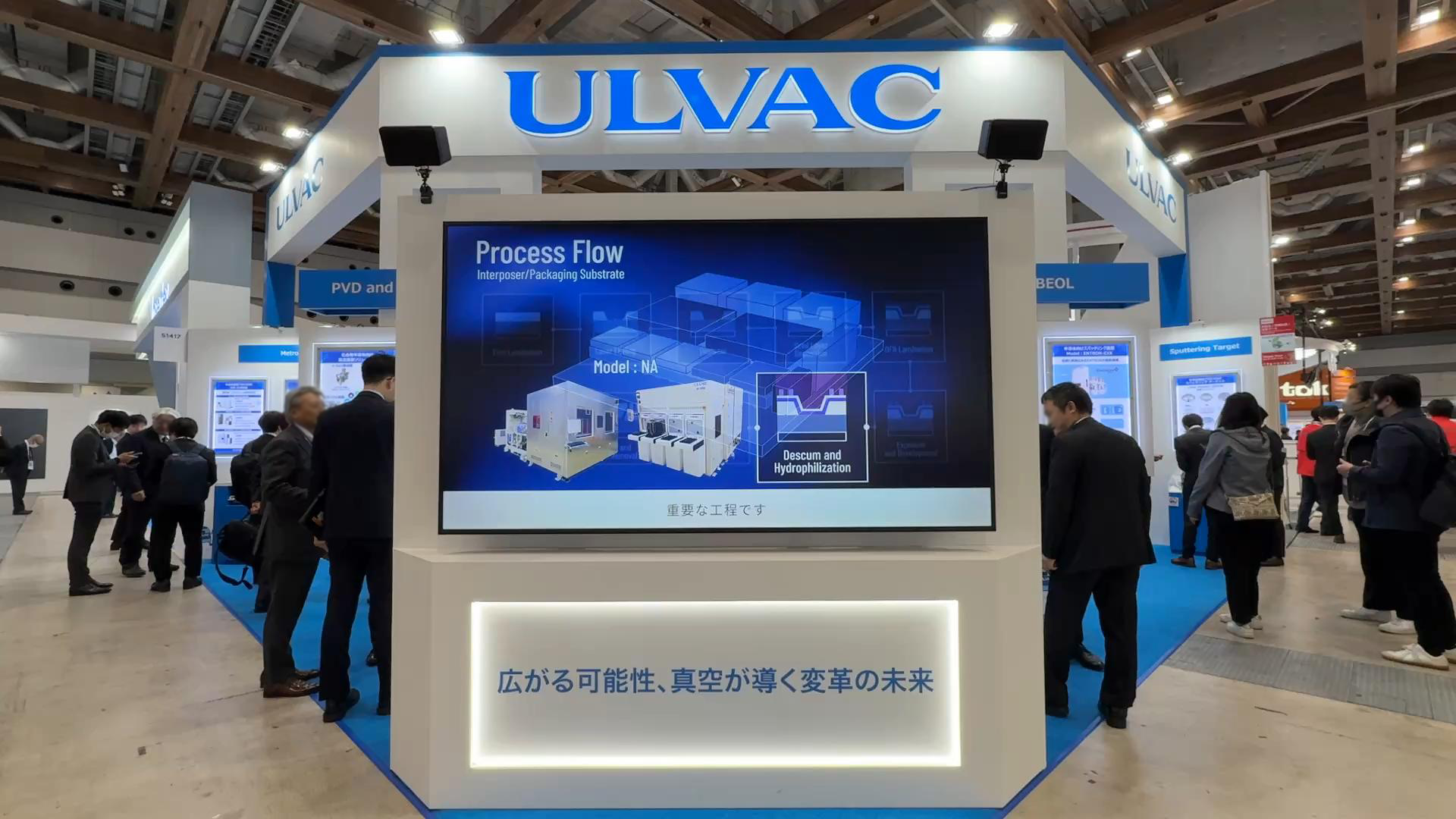

スマートフォンや自動車、AIなど、私たちの身近な製品を支える半導体。2025年12月17日~19日、その最前線が集まる展示会「SEMICON Japan 2025」が東京ビッグサイトで開催されました。

アルバックは、半導体製造の前工程(南館)と後工程(東館)の両方にブースを出展し、装置・材料・ポンプなどを"つながり"で見せる展示に挑戦しました。会場の空気感や人気のコーナー、来場者のリアルな反応をわかりやすく紹介します。

SEMICON Japanってどんなイベント?

SEMICON Japanは、半導体を「つくるための技術、装置、材料など」が一堂に会する、国内最大級の展示会です。製造装置メーカーや材料メーカー、研究機関、受託企業などが最新動向を発信し、会場での対話をきっかけに新たなコラボレーションが生まれることも少なくありません。前工程と後工程の両エリアに出展することで、半導体製造の幅広い工程をカバーしている点を、展示内容だけでなく会場内の動線そのものでも表現しました。

展示の見どころ:今年のアルバックは"つながる展示"

今年多かったのは、「単品の性能」よりも技術の組み合わせへの関心です。たとえば、

プロセス×材料 新しい材料とプロセスを組み合わせると、品質を左右する薄膜をより薄く均一な膜を短時間で作れる可能性。

装置×運用 日々の運転・保守データを活用し、止めない・劣化させないための運用工夫。

将来ロードマップ 「この先5年で、どう進化していくのか」という質問も多く、未来志向の対話が目立ちました。

会場の手ざわり:熱量ある来場者と"伝える力"の鍛錬

会場は国内を中心に多くの来場者が訪れ、例年以上の活気に包まれていました。展示では、開発の背景や応用分野まで踏み込んだ説明が好評。会話を重ねる中で、

社外から自分たちの技術が受け止められているのかを知る機会に。

若手メンバーにとっては、専門外の方にも伝わる説明の仕方を磨く実践の場に。

SEMICON Japanは、技術を「見せる」だけでなく、対話を通じて理解と共感を育てる場であることを、改めて実感しました。

その場で「なるほど」、投資家向けブースツアー

会場では、投資家向けの説明ツアーも実施しました。実物を見ながら事業や技術のポイントを説明することで、理解のスピードと深さが大きく変わります。メインの半導体前工程に加えて、パッケージング分野、プラズマ技術、アッシング装置など、アルバックのコア領域を俯瞰的に紹介。その場での反応や質問は、今後の情報発信を考えるうえでも貴重なヒントとなりました。

学生と向き合う「未来カレッジ」

SEMICON Japanと同時開催された、学生向けイベント「未来カレッジ」にも参加しました。会社概要の説明に続き、技術系の仕事の進め方やキャリアについて具体例を交えて説明。海外出張の頻度や英語への不安など、率直な質問も多く、次世代を担う学生たちの関心の高さがうかがえました。半導体業界を、より身近な選択肢として感じてもらうきっかけになったようです。

次回は、あなたも会場で

SEMICON Japanは、アルバックが取り組む"つながる真空技術"を体感できると同時に、業界や市場の空気を肌で感じられる貴重な場です。次回はぜひ、会場で実物を見て、スタッフに話しかけてみてください。きっと、ニュース記事だけでは気づけない「なるほど」に出会えるはずです。

CTOオブ・ザ・イヤー2025 特別賞受賞

2025年10月、当社常務執行役員であり、開発本部長兼コンポーネント事業本部長の清田淳也が、テクノロジー専門メディア「日経クロステック」が選ぶCTOオブ・ザ・イヤー2025特別賞を受賞しました。

この賞は、各分野で目覚ましい活躍をしているCTO(最高技術責任者)を選出し、その功績を讃えるものです。今回、当社が強みとする真空技術をコアに、半導体や電子部品の製造装置の競争力向上にとどまらず、医療や量子コンピューターなど新しい分野への挑戦を続けている姿勢が高く評価されました。

具体的な取り組みとしては、

血液をパウダー化して長期保存するバイオ・メディカルソリューション

量子コンピューター向け冷凍機の開発など、真空技術の新しい応用に挑戦しています。

日経表彰

さらに、AI技術を積極的に取り込み、プラズマ技術と組み合わせて半導体向けプラズマプロセス装置の性能向上を目指しています。

ディスプレイ分野で培った技術の水平展開も評価ポイントです。当社は、酸化物半導体(IGZO)用の成膜装置(スパッタリング装置)をディスプレイ向けに開発してきましたが、この技術を最先端半導体向けに応用し、実用化しました。これは、東京科学大学(旧東京工業大学)の細野秀雄教授との長年の共同研究の成果です。同大学のキャンパス内には「アルバック先進技術協働研究拠点」を設立し、次世代技術のシーズ探索を進めています。

さらに、大阪大学や米IBMとの連携を通じて、バイオ・メディカルソリューションや量子コンピューター技術の開発も加速しています。

審査会では、こうした取り組みについて「コア技術を水平展開し、産学連携を通じて外部の力を活用するという点で、まさにCTOらしいCTOだ」という評価が寄せられました。

今回の受賞は、挑戦する姿勢と技術革新を続ける当社の取り組みが認められた証です。これからも、技術革新を通じて産業の未来を切り拓いていきます。

「マイクロパウダードライ法による赤血球の保存特性に関する検討」について、学会誌「表面と真空 (Vacuum and Surface Science)」に論文が掲載されました。

凍結乾燥(フリーズドライ)は、輸血用血液製剤を保存するために検討が進められている方法ですが、従来法では細胞が傷つき、赤血球が壊れることが課題でした。

本研究では、赤血球の凍結乾燥法としてマイクロパウダードライ法と従来の緩慢凍結乾燥法を比較し、乾燥直後と冷蔵(2℃)・室温(28℃)で1か月保管後の水分量と赤血球が壊れた割合を調べました。結果として、マイクロパウダードライ法は乾燥直後の赤血球は壊れた割合が低く、1か月後も両指標の変化は小さく、両温度条件で比較的安定していました。この結果はマイクロパウダードライ法により従来以上の長期間の赤血球保存が実現できる可能性を示唆しています。

アルバックは、マイクロパウダードライ技術の適用範囲を広げ、医薬品にとどまらず、さまざまな分野で安定した粉体の製造・保存に役立てられるよう、今後も検討を進めます。

掲載誌

表面と真空 69巻(2026)2号 https://www.jstage.jst.go.jp/browse/vss/-char/ja/ (本文は購読者のみアクセス可能です。)

お問い合わせ先

株式会社 アルバック 未来技術研究所 e-mail:uj_mirai@ml.ulvac.com

株式会社アルバック(以下、ULVAC)は、Taiwan Semiconductor Manufacturing Company(以下、TSMC)より「2025 TSMC Excellent Performance Award」において「Excellent Production Support」表彰を受賞しました。

本賞は、TSMCのサプライチェーンの改善・効率化に大きく貢献したサプライヤーに贈られるものです。 このたび当社グループは、生産能力の拡大を含む優れた生産サポートを提供した点に加え、研究開発との強固な技術協業を推進した点が高く評価され、受賞に至りました。

当社グループは本受賞を励みに、装置サプライヤーとしての使命を果たすとともに、半導体業界の発展に貢献してまいります。

UTH 20周年!仲間と歩んだ感謝の一日

2025年12月19日、アルバックタイランド(UTH)は設立20周年を迎え、記念式典を開催しました。この日は、UTH社員にとって大きな節目。社員全員で、これまでの歩みを振り返り、未来への希望を語り合う特別な時間となりました。

仏教式の祈りからスタート

式典は、社員と会社の幸運を祈る仏教式の行事で幕を開けました。静かな祈りの時間を通じて、これまで支えてくれた仲間や地域への感謝の気持ちを改めて感じることができました。

笑顔あふれるパーティ

その後は、全社員が集まる温かいパーティへ。食事を楽しみながら、思い出話や未来の夢を語り合い、会場は笑顔でいっぱいに。20年という長い時間を共に歩んできた仲間との絆を再確認するひとときでした。

未来への力強いメッセージ

式典では、取締役のタナチャイ氏が「UTHは過去20年間、社員と経営陣の努力で成長を続けてきました。これからも東南アジアで無限の可能性を追求し、さらなる高みを目指します」と力強く宣言。

新たな挑戦への意欲が会場に広がりました。この記念すべき日を通じて、社員一同「チームワーク」「献身」「思いやり」が会社の成長を支えてきたことを改めて実感しました。

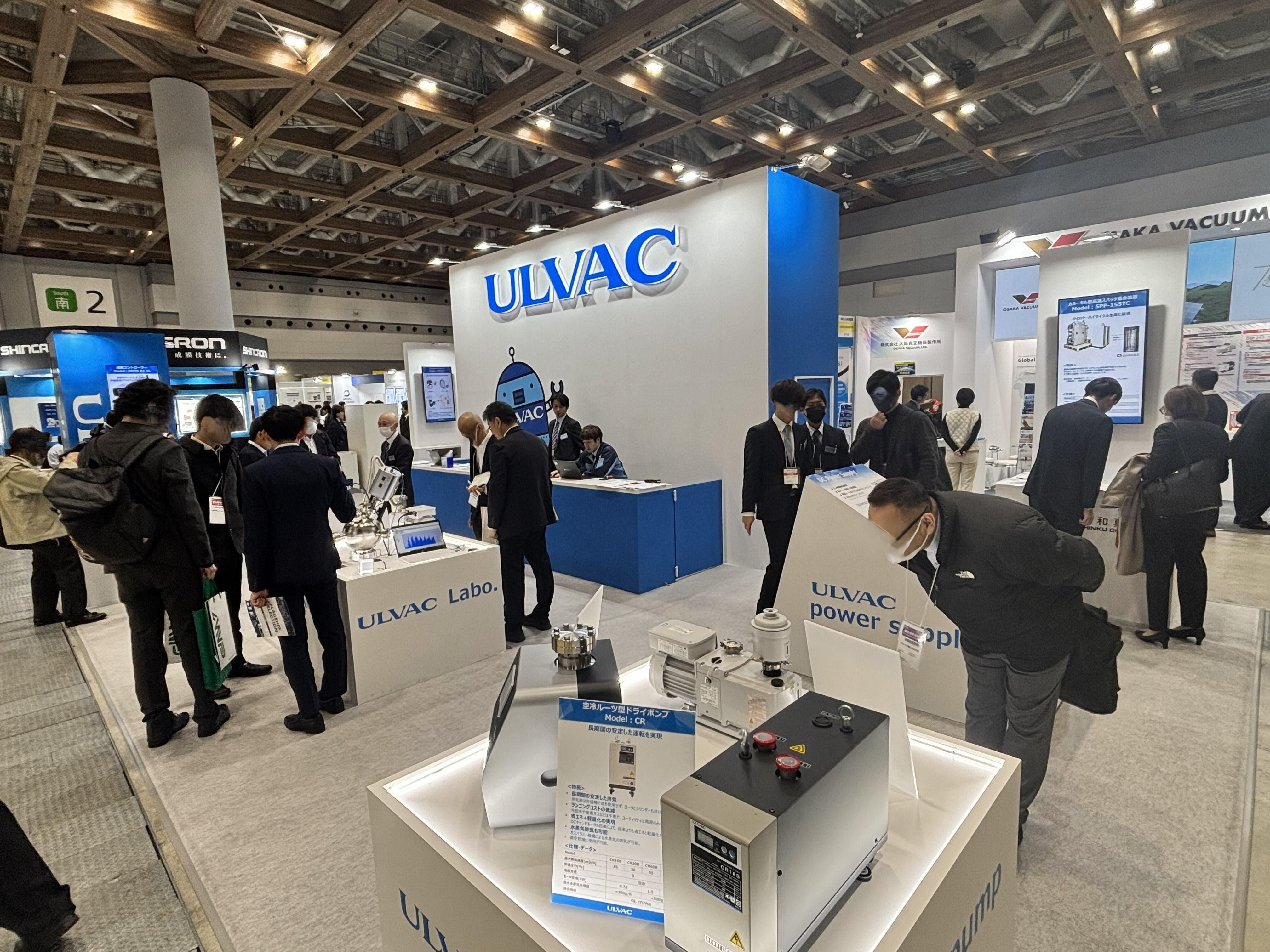

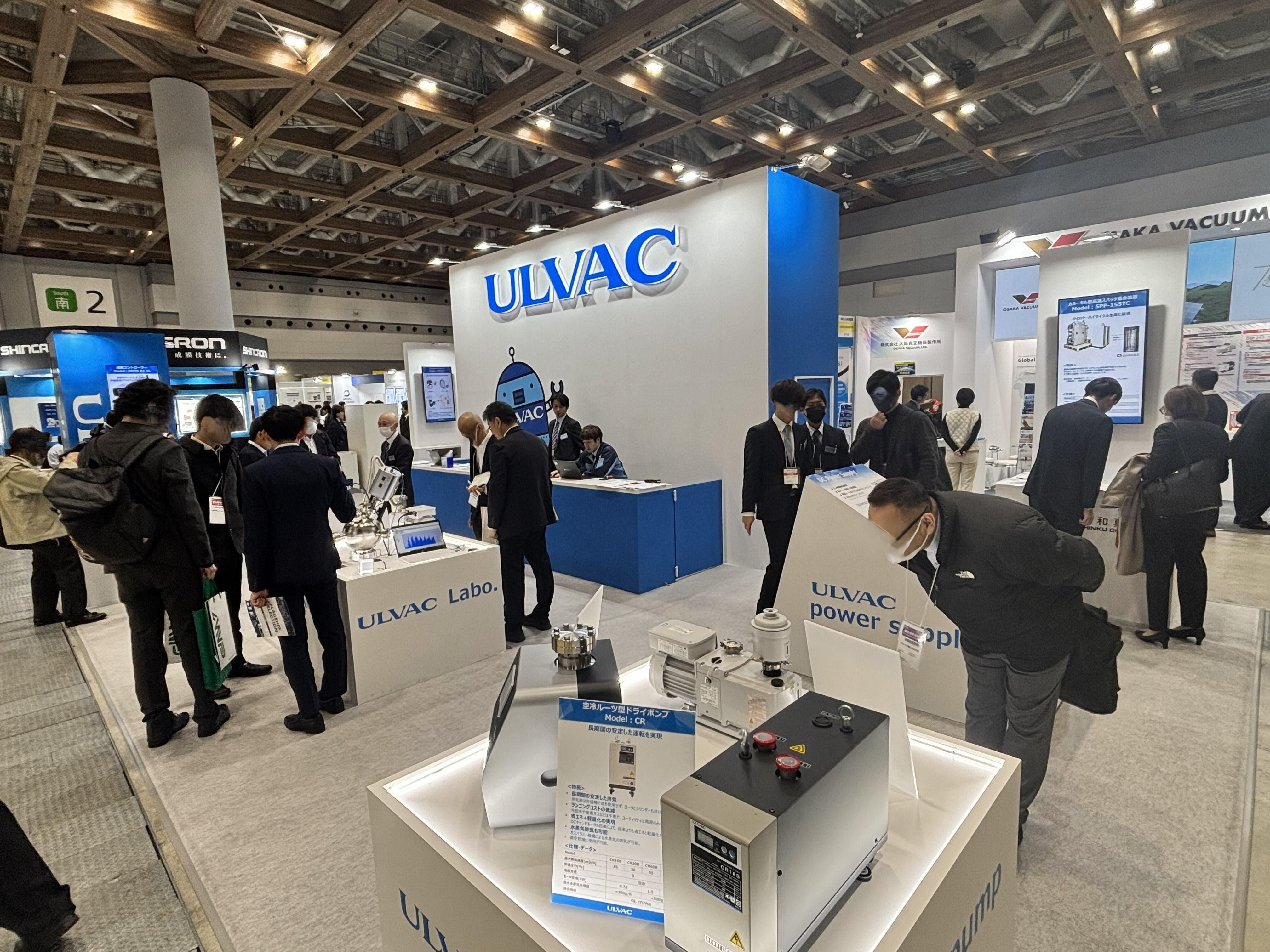

2025年12月3日~5日、東京ビッグサイトで「VACUUM真空展2025」が開催されました!

この展示会は、真空技術を支える機器や装置が一堂に会する、日本最大級の真空技術イベント。半導体や分析、研究分野など、さまざまな現場で活躍する技術を身近に感じられる場として、毎年多くの来場者でにぎわいます。今回は、当社ブースでのインタビューを通して、会場の雰囲気や見どころ、来場者の反応をご紹介します。

会場は想像以上のにぎわい

会期中は想像以上の来場者数で、会場は終始活気にあふれていました。半導体関連をはじめ、幅広い業界の方が足を運び、真空技術への関心の高さを改めて感じる3日間に。 学生向けの見学ツアーも行われ、将来この分野を目指す若い世代の姿も見られました。

ぐっと入りやすく進化したアルバックブース

今回のアルバックブースは、デザインを大きく刷新。梁をなくした開放的なレイアウトにすることで、自然と足を運びやすい空間を目指しました。さらに、ブース内にはラボスペースを新設。 ポンプの実稼働やリークチェック、ガス分析の様子をその場で見られる"ライブデモ"は、「説明を聞いてすぐ体感できる」と多くの来場者から好評でした。

見て・触って楽しめる展示ラインアップ

電源(PowerSupply) 実際の電源モックを使い、操作感や設定の流れをその場で体験できる展示に。「見て、触る」ことで理解が深まります。

ポンプ(Pump) 新型ポンプ「Gv200」は、実際に動かして静音性を体感できる展示に。新モデルの「Desktop YTP」も実機展示され、ブース内でも特に注目を集めていました。

計測(Measurement) 真空計、リークディテクタ、分析計をまとめて展示。新モデル「HELIOT MONO」を含め、装置への組み込みイメージがしやすい構成で、多くの質問が寄せられました。

ULVAC CRYOGENICS 空気から液体窒素を作り出す液体窒素ジェネレーターの実機展示も人気。研究用途から産業用途まで、幅広い可能性に関心が集まりました。

印象的だった出来事も

展示期間中には、なんと「くまモン」がアルバックブースを訪れるサプライズも。名刺交換をする微笑ましい場面に、ブース周辺は和やかな雰囲気に包まれました。3日間を通じて、予想を上回る反響があり、来場者の皆さまに真空技術をより身近に感じていただけた展示会になったと感じています。

九州工場で音楽と笑顔が響いた日!

アルバック 九州工場(鹿児島県霧島市)が主催する音楽イベントが、 工場近くの霧島市立安良小学校体育館で開催されました。 社員やご家族、地域の皆さま、そして安良保育園の園児たちを含め、約50名が参加。 朝から子どもたちの元気な声が響き、会場はあたたかな雰囲気に包まれました。

金管五重奏でスタート!

最初のプログラムは、鹿児島県文化振興財団の登録アーティストによる金管アンサンブル演奏。 NHK大河ドラマのテーマ曲など、誰もが知っている曲が並び、 子どもも大人も自然とリズムに乗って楽しんでいました。

安全講話&体験コーナー

霧島警察署の警察官による安全講話では、飲酒運転の危険性や特殊詐欺への対策など、 生活に役立つ情報をわかりやすく紹介。 さらに、酔った状態を疑似体験できるゴーグルやパトカー試乗など、 普段できない体験に参加者も大興奮! マスコットキャラクター「よこがワン」も登場し、会場は笑顔でいっぱいになりました。

真空実験で科学を体感

アルバックの技術を紹介するコーナーでは、真空の不思議を五感で体験できる実験を実施。 クイズを交えながら進行し、笑いあり学びありの時間に。 参加者からは「アルバックの技術を身近に感じられた!」との声も。

最後は豪華景品の抽選会

スマートウォッチや防災セットなどが当たる抽選会は、 番号が呼ばれるたびに歓声が上がり、最後まで大盛り上がりでした。

今回のイベントで一番印象的だったのは、 地域の皆さま、社員とご家族、そして子どもたちが同じ空間で笑い合えたこと。 工場と地域の絆がさらに深まった一日となりました。

アルバックは、2026年度も引き続き大阪大学と博士人材育成に取り組みます。 このプロジェクトは、大学と企業が協力し、未来を担う研究者を育てることを目的としています。私たちは、産学連携を通じて社会に新しい価値を生み出すことを目指しています。

活動のポイント

この取り組みの中心となるのは、大阪大学の「未来基金」への寄付です。これにより、研究と教育の両面で連携を強化しています。大学の最先端研究と、アルバックが長年培ってきた産業技術を組み合わせることで、社会課題を解決し、新しい価値を創出することを目指しています。こうした協力関係は、単なる資金提供にとどまらず、知識と技術の融合によるイノベーションを促進します。

なぜ博士人材育成が重要なの?

博士課程の学生や研究者には、深い専門知識だけでなく、産業界で求められる実践的な課題解決力が必要です。このプロジェクトでは、学術と産業をつなぐ次世代の人材を育成することをめざしています。産業界で活躍できる博士人材を育てることは、日本の技術力強化にもつながります。

これまでの成果

これまでに、多くの博士課程の学生が学会や国際会議で成果を発表しました。さらに、共同研究から新しい研究テーマが生まれ、外部資金の獲得にもつながっています。 こうした成果は、大学と企業の双方にメリットをもたらし、「双方向型の共創モデル」として定着しつつあります。このモデルは、研究と産業の距離を縮め、イノベーションを加速させる重要な仕組みとなっています。

これからどうなる?

2026年度は、これまでの成果をさらに発展させ、博士人材育成とオープンイノベーションを両立させる取り組みを続けます。未来基金を通じた支援により、産学連携をさらに深め、社会に貢献する研究を推進します。 興味のある方は、大阪大学の未来基金サイトもぜひチェックしてみてください!

関連外部サイト

大阪大学の未来基金について

https://www.miraikikin.osaka-u.ac.jp/greeting

大阪大学未来基金 「産学官共創による工学博士人材育成事業」