2025年7月26日(土)、やどりき水源林*1にて、当社が取り組む森林再生プロジェクト*2が開催されました。今回は従業員とそのご家族、総勢25名が参加し、自然とふれあいながら学びと体験を深める一日となりました。

森林が育む「水のちから」を体験

活動の中心となったのは、「水源涵養(かんよう)機能」を学ぶ実験です。これは、森林が雨水を蓄え、ゆっくりと地中に浸透させることで、川や地下水の水量を安定させる働きのこと。実験では、荒れた森林と保全された森林を模したキットに水を流し、流れ方や水の色・量の違いを観察しました。

子どもから大人まで、目で見て体験することで、森林が私たちの生活を支えていることを実感。水不足や洪水といった問題が、森林の状態と密接に関係していることを学びました。

汗を流して、森を守る

実際の間伐作業にも挑戦。枝打ちや間伐は、森林の健全な成長を促すために欠かせない作業です。参加者の皆さんは汗をかきながらも、達成感に満ちた表情で作業を終えました。

清流に生きる命との出会い

寄沢の清流では、水生生物の観察も行いました。インストラクターの解説を受けながら、「きれいな水」に生息するサワガニやカジカを実際に観察。水質と生物の関係を学ぶ貴重な機会となりました。

夏の思い出と、未来への一歩

昼食後にはスイカ割りも行われ、子どもたちの笑顔があふれるひとときに。暑い日ではありましたが、森林の心地よい風の中で過ごした時間は、夏休みの楽しい思い出となったことでしょう。

私たちは、こうした活動を通じて、次世代に豊かな自然環境を引き継ぐことを目指しています。今後も従業員の皆さんとともに、森林保全に積極的に取り組んでまいります。

参考情報

*1)やどりき水源林

神奈川県松田町寄に広がる約529haの森林で、神奈川県が管理し、公益財団法人かながわトラストみどり財団が運営協力しています。 水源涵養や自然体験の場として県民に親しまれています。

*2)森林再生プロジェクト

本社・工場が立地している神奈川県の森林は、全国平均に比べて非常に少ない数値となっています。 神奈川県では、水源林の役割を持つ森林の豊かな恵みを次の世代に引き継ぐための整備活動が行われています。 この取り組みに賛同し、神奈川県が推進する「森林再生パートナー」制度に2022年6月から参画しています。 本制度による森林整備を通して算定されるCO₂吸収量は、5年間で247tになります。 地球にやさしく持続可能な社会づくりに貢献するという2050年にありたい姿の実現に向けて、環境活動に取り組んでいます。

エッチングとは、半導体製造工程において半導体上の不要部分の薄膜を加工する技術である。薄膜上のマスクのパターンを転写することであり、マスクに覆われていない部分の薄膜を一部または全部除去する工程のことを指す。

ドライエッチングでは、一般的に誘導結合プラズマ (ICP, Inductively Coupled Plasma) や容量結合プラズマ (CCP, Capacitively Coupled Plasma) などの真空放電プラズマを用いる。

エッチング対象物に対して反応性を有するガスのプラズマを生成し、処理基板にバイアスを印加することでプラズマ中の反応性イオンを基板表面に引き込み、エッチングを促進する。反応性イオンエッチング (RIE, Reactive Ion Etching) とも呼ばれる。より速く異方性をもってマスクのパターンを薄膜に転写できる。そして、薄膜材料 (固体) を化学反応によって気体として排気するため、真空容器中への薄膜元素の蓄積を抑制でき、エッチングの長期動作安定性が高い。それらの特徴によって、半導体・電子部品の製造工程で重要な役割を果たしている。

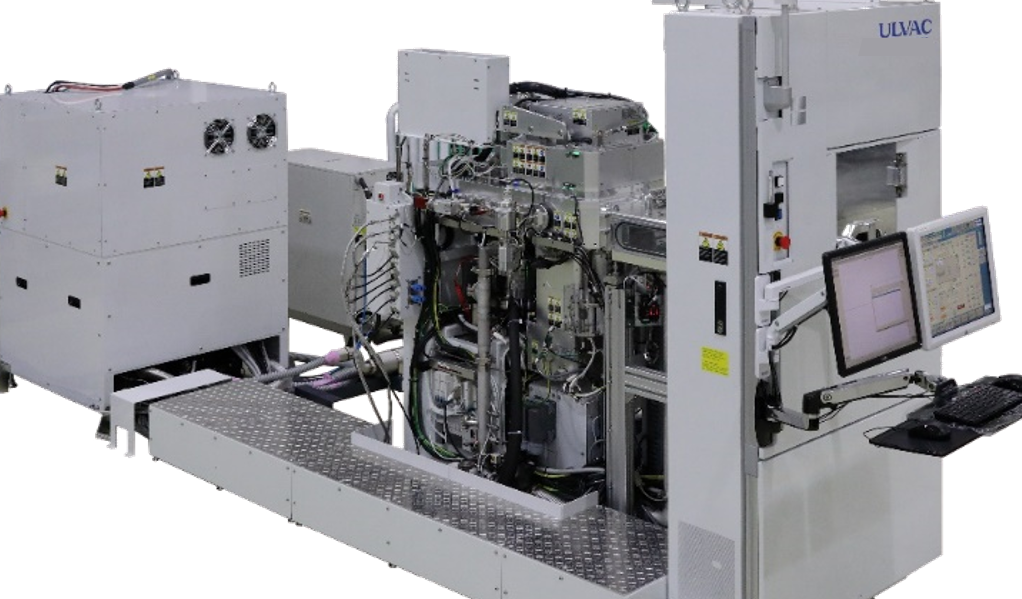

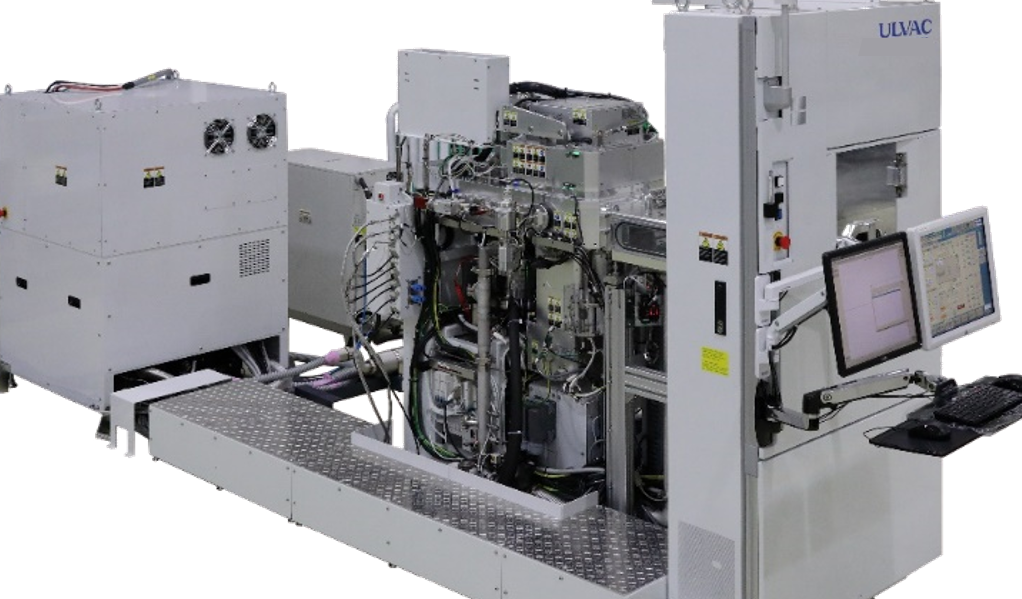

エッチング装置の紹介はこちら

意外と知らない真空用語解説一覧

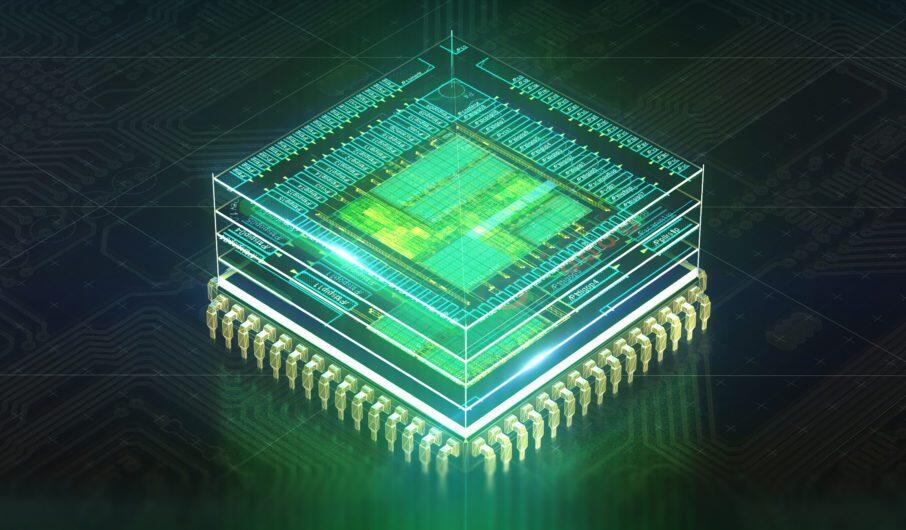

光学多層膜はガラスや樹脂,金属などの基材に数種類の屈折率の異なる材料を交互に形成することで特定波長の光を透過・反射する機能をもたせた薄膜である(Fig.1)。かねてよりレンズの反射防止膜や増反射ミラーなどで使用され,光学フィルタやハーフミラーなど応用例は多岐にわたる。

光学薄膜の原理

また,近年では3D顔認証用のセンサー,距離計測用のLiDAR(Light Detection and Ranging),生体認証などのデバイスにも光学薄膜が活用されている。これらのデバイスではFig.2に示すように,光源から特定の波長の光を対象物に照射し,対象物から反射してきた特定波長の光のみを検出するため,BPF(Band Pass Filter)が用いられている。特に,顔認証用途の近赤外BPFは,広い視野角にわたって信号損失を少なくするため,対象物からの反射光が大きな角度で入射した場合でもBPF透過帯の中心波長のオフセット量が小さく,高透過率のものが求められる。

BPF(バンドパスフィルター)の原理

そのため,これまで主に使用されてきた高屈折率成膜材料のTa 2 O 5 ,Nb 2 O 5,TiO 2に比べて,近赤外波長領域での屈折率が高く可視光波長領域を吸収する特性をもつ水素化アモルファスシリコン(a-Si:H)を使用したBPFが注目されている1 )。a-Si:Hを使用することでBPFの膜層数,膜厚の低減が可能となり生産性の向上が期待される。

また,Fig.3に示すようにスマートフォンのカメラモジュールなどは,従来レンズや光学フィルタなどの光学部品とCMOSなどの半導体部品を別々に製造後,モジュールとして組み立てを行っていたが,今後ウェーハレベルで各部品を作製,貼り付けを行った後にカットするWLO(Wafer Level Optics)と呼ばれる製造方法が主流になると言われている。そのため,φ200 mm,φ300 mm ウェーハへの対応,品質面においても従来より低パーティクル装置・ハンドリング管理の対応が求められる。光学膜の成膜方法としては蒸着が用いられてきたが,光学膜の用途が広がるにつれ膜厚制御性や面内分布の要求がより高度になり,スパッタ法による光学膜の成膜に注目が集まっている。

光学デバイスの製造プロセス

記事の続きは下記URLよりアルバックテクニカルジャーナルに

ユーザ登録するとご覧いただけます。

https://www.ulvac.co.jp/r_d/technical_journal/tj84j/

本研究は,文部科学省『省エネルギー社会の実現に資する次世代半導体研究開発』事業JPJ005357ににおける名古屋大学殿の協力機関としての成果が含まれる。本事業では,次世代半導体材料として有望な窒化ガリウム(GaN)に関して,材料創製からデバイス動作検証・システム応用までの研究開発を一体的に行う研究開発拠点を構築し,理論・シミュレーションも活用した基礎基盤研究を実施することにより,実用化に向けた研究開発を加速することを目的としている。

GaNパワーデバイスの低ダメージドライエッチング技術

近年の飛躍的な科学技術の進歩に伴い,エネルギー消費量は世界的にますます膨大になっている。一方で,エネルギー発電やガソリン自動車等から排出される二酸化炭素(CO2)や温室効果ガスが環境に与える影響は甚大であり,地球温暖化防止,省エネルギー化を目指した研究開発がとても重要になっており,喫緊の課題である。

GaNは,現在半導体パワーデバイスの主流となっているシリコン(Si)に比べて,バンドギャップエネルギー及び絶縁破壊電界強度が大きく,また電子移動度が高く,優れた基礎物性を有している。そのため,GaNは低損失かつ高耐圧パワーデバイスとして,特に環境負荷軽減となるハイブリッド電気自動車(HV)や電気自動車(EV)への応用が期待されている。

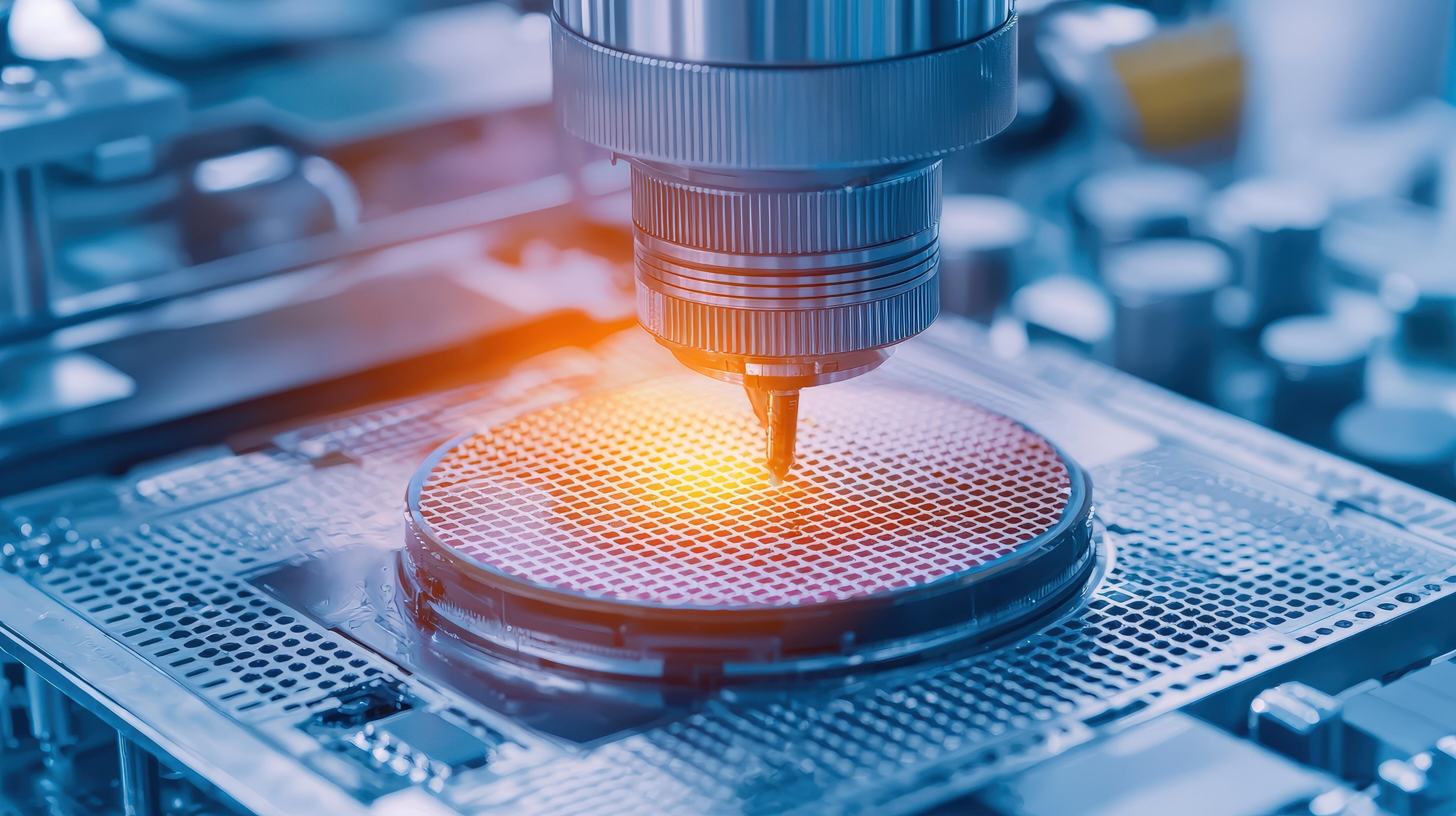

GaNを用いたパワーデバイスには,様々な素子構造の研究開発が進められている1 )。その中でも,デバイス構造の特徴から縦型トレンチゲートMetal-oxidesemiconductor field-effect transistors( MOSFETs)は,チップの小型化と高速スイッチングを可能にするデバイスとして注目されている。トレンチゲートという名称の通り,GaNウェーハ表面に,幅・深さが1 μm程度の溝(トレンチ)を形成することで,デバイスのオンオフのスイッチング動作を行うゲートとして機能させる。

トレンチは,エッチング工程により形成される。その側壁はデバイス動作時に反転層として電子が流れる経路となる。そのため,垂直性及び側壁表面の平坦性が良好なトレンチを形成するエッチング技術は,特にチャネル移動度というデバイス評価指標を向上させるための必須の技術となる。また,トレンチ形成の際に導入されるGaNへのダメージの低減も重要な課題である。

本報告では,GaNトレンチ形状制御と低ダメージ化に向けた最近のアルバックの取り組みと得られた成果を紹介する。

(※この記事は、2021年4月発行のテクニカルジャーナルMo.84に掲載されたものです。)

記事の続きは下記URLよりアルバックテクニカルジャーナルに

ユーザ登録するとご覧いただけます。

https://www.ulvac.co.jp/r_d/technical_journal/tj84j/

文 献

1) T. Kachi: Jpn. J. Appl. Phys. 53, 100210( 2014).

ガス種・流量比、プロセス圧力、RFパワー等のプロセスパラメータ最適化は、エッチングレート・選択比・加工形状といった項目だけでなく、面内分布にも影響します。したがって、プロセスによる分布追求には、他の項目とのトレードオフが発生します。

分布追求をプロセスではなく、ハードで行う場合、アンテナ構造や電極間距離の最適化で対応可能ですが、装置仕様を決めてしまうため、トレードオフの関係は解消されません。

ULVACが提案する新プラズマ源「ISM-duo」ならプロセスパラメータそのままに、分布のみ最適化可能です。

新プラズマ源「ISM-duo」の特徴

従来のISMプラズマ源が持つ高密度プラズマの特徴に加え、ISM-duoプラズマ源はRFパワー分配ユニットを搭載しています。内・外周のICPアンテナへ 任意にRFパワーを分配することで、エッチング面内分布の制御が可能になります。

※ISM:ICP with Static Magnetic field duo:distribution uniformity optimizable

ISM-Duoコンセプト

エッチング面内分布最適化の一例 (プロセスパラメータ同条件下での比較)

半導体パッケージ(実装)分野でよく使われる略語/用語の一覧です。

単語

正式名称

内容

A

ABF

Ajinmoto build-up film

味の素ファインテクノ製のBuild-up film。業界シェアが100%に近い。

AM

Acoustic Microscopy

超音波顕微鏡

AiP

Antenna in Package

アンテナとRF chipを同一に実装する方法

AP / アプリケーションプロセッサー

Application processor

通信通話以外のオペレーション以外の動作を行うデバイス

アクセラレータ

サーバーの処理能力を向上させるツール

B

BEOL

Back end of line

半導体チップに配線を形成する工程

BGA

Ball grid array

パッケージ裏面にSolder bumpを格子状に規則的に並べた構造

Bridge

微細パターンが形成されたSi bridgeによって、ChipとChipを接続した実装方法。Si interposerをLocalに導入した実装方法。

Build-up配線

Build-up配線を用いた配線。基板の配線層に用いられる。

Build-up film

Build-up配線に用いられるフィルムで、樹脂とシリカフィラーの混合材料からできている。

C

カーボンニュートラル

温室効果ガスの「排出量」から、植林などによる「吸収量」を差し引いて、合計を実質的に"ゼロ"にすること。

Cavity flame core

PoPの上側と下側を繋ぐMetal配線が形成された積層基板 Samsungの技術

CCD

core complex die

CCD

CPU compute die

CF

Chip first

Fan-Out工程で、Chipを先にMountし、後でRDLを作製する方法

Cube

Samsungの2.5D実装の呼称

Chip First

Fan-Outで、チップを先に仮固定ウエハして再配線を形成する手法

Chip Last

Fan-Outで、再配線層を先に形成して、チップを固定する手法

Chiplet

半導体チップをそれぞれ製造して、後から配線ロスが極力減るように組み合わせる技術

CL

Chip last

Fan-Out工程で、RDLを先に形成し、後でChipをMountする方法

CMOS

complementary metal oxide semiconductor

Co D2W

Collective die to wafer

CoW

Chip on Wafer

CoWoS

Chip on Wafer on Substrate

tsmcの2.xD実装技術の呼称

CoWoS-S

tsmcの2.5D実装技術の呼称 Si interposerを使用。

CoWoS-R

tsmcの2.1D実装技術の呼称 Organic interposerを使用。

CoWoS-L

tsmcのBridgeを用いて2.xD実装 Local Si bridgeを使用。

COP

Co-packaged Optics

フォトニクス装置と電子スイッチを1つのパッケージにまとめ、信号の高速化や消費量削減や熱効率低減を目的としたパッケージ技術

CPU

central processing unit

周辺機器などからデータを受け取り制御・演算を実施するデバイス

CSP

Chip Size Package

半導体チップの大きさと同等レベルのパッケージ

D

データセンター

サーバーやネットワーク機器を設置するために特化した建物

DB

Debonding

基板接着されたチップ、または、接合されたウエハから、チップまたはウエハを剥離すること

DBG

Dice before grind

DBHi

direct bonded heterogeneous integration

IBMのBridge構造 ChipにBridgeを先に接続し、基板へ搭載

DBI

direct bond interconnect

Descum

フォトリソ工程後の残渣をScumと呼び、除去する工程をDescumという。

Desmear

レーザードリル工程後の残渣をSmearと呼び、除去する工程をDesmearという。

DTC

Decoupling capacitor

再配線層のノイズを目的としたSi Viaに形成されたCapacitor。

DP D2W

Dilect placement die to wafer

E

ECD

Electrochemical deposition

電界めっき工程

EFB

Elevated Fan-Out Bridge

AMDのFan-OutとBridgeを組み合わせた実装構造

EFI

embedded fine interconnect

IMEのBridge構造

EMIB

Embedded Multi-Die Interconnect Connect Bridge

IntelのBridgeを用いた実装方法。基板にBridgeを埋め込み、その後チップの搭載を行う。

F

Fabless

自社で製造ラインを持たず、FoundryまたはOSATに生産委託しているメーカー

Face up

Fan-Outの工程で、Padを上向きに搭載し実装する方法 InFOはChip firstのFace up工法

Face down

Fan-Outの工程で、Padを下向きに搭載し実装する方法

FAB

Fast atom beam

高速電子ビーム

FCBGA

Flip chip ball grid array

Flip chipを用いたBGA

FEOL

Front end of line

半導体チップのウエハ上に素子を形成する工程

FI

Fan-In

WLPの別名。Fan-Outに対する呼び方。

FO

Fan-Out

半導体チップに対して、取り出し口が広がっている構造。チップに対してBump数を増加することができる。

FOCoS

Fan-Out Chip on Substrate

ASEのTSV less Heterogeneous integration

FOEB

Fan-Out Embedded Bridge

SPILのBridgeを用いたFan-Out製品。

FOD

Film over die

FOPoP

Fan-Out Package on Package

Fan-Outのパッケージの上に異なるデバイスを搭載すること。

Foverous

Intelのチップの積層技術

Foverous-Omni

Intelのチップの積層技術 はんだBump-はんだBump

Foverous-Direct

Intelのチップの積層技術 Cu-Cu

Foundry

半導体チップの製造を請け負うメーカー

FC

Flip chip

半導体チップを切り出して、反転(Flip)して実装する方法

G

GAFA

米国のIT関連企業大手4社の頭文字をとった造語 Google, Apple, Face book, Amazon

GPU

graphic processing unit

画像処理に特化した演算を実施するデバイス

GX

グリーントランスフォーメーション

太陽光発電や風力発電といったグリーンエネルギーへの転換により、産業構造や社会経済を変革し、成長につなげること

H

Homogeneous integration

同種のチップを同一配線層で接続する実装方法

Heterogeneous integration

異種のチップを同一配線層で接続する実装方法

HAZ

heat affected zone

HDI

High density interconnect

HPMJ

high-pressure microjet

HPC

High performance computing

HBM

High Bandwidth Memory

DRAMが積層されたメモリー

HMC

Hybrid memory cube

Hybrid bonding

Bumpレス直接接合技術。Cu-Cuと絶縁膜-絶縁膜の直接接合。

Hybrid bonding Collective

仮固定ウエハを用いたHybrid bonding / アライナーで位置合わせする。

Hybrid bonding Suquential

Die bonderを用いたHybrid bonding

I

IDM

Integrated Device Manufacturer

設計・製造・組み立て・検査・販売を一貫して自社で行えるデバイスメーカー

IMT / 挿入実装

Insertion Mount Technology

プリント基板の内部にデバイスを実装する方法

I/O

Input / Output

Interposer

2.xD実装で使われるシリコンダイと樹脂基板間の配線基板

InFO

Integrated Fan-Out

tsmcのFan-Out技術の呼称

InFO oS

InFO (assembly) on Substrate

複数のChipをRDLで並列に繋ぎ、基板へ接続するInFO製品。

InFO B

InFO PoPの下側だけの状態。OSATの方で、上側のデバイスを接続する。

i-THOP

integrated Thin film High density Organic Package

新光電気の2.3Dパッケージ基板 アイソップ

J

JIEP

実装エレクトロニクス実装学会

K

L

LAB

Laser Assisted Bonding

レーザーによってチップまたはウエハを基板に接着する工程

LAL

light absorber layer

LDB

Laser debonding

レーザーによってチップまたはウエハを基板から剥離する工程

LDI

Laser direct image

LG

Laser groove

Lead

樹脂から露出している外部配線

LF

lead flame

半導体チップを支持・固定する役割をに担う、パッケージから露出している複数の外部接続端子

M

メタバース

自分のアバターを作成し行動することができるインターネット上の仮想空間

MCM

Multi chip module

チップを複数個搭載したモジュール

MIMO

Multiple Input and Multiple Output

送信機と受信機の双方で複数アンテナを用いる送受信技術

Mooreの法則

ムーア氏が発表した「半導体回路の集積密度は1年半~2年で2倍となる」という経験則

More Moore

スケーリングによらない、トランジスタの性能向上 (立体構造化など)

More then Moore

異種デバイスを集積して高性能化すること → SoC & SiP

N

O

oS

on Substrate

CoWをSubstrateに載せる工程

OSAT

Out Source Assembly and Test

実装工程の製造を請け負うメーカー

P

プロセスノード

一般的にトランジスタMOSFETのゲート配線の"幅"、または"間隔"を指す

PDB

Photonic debonding

PoP

Package on Package

パッケージの上にパッケージを積層させること。パッケージを重ねることでデバイス内のパッケージの占有面積を減らす。

PP

Prepreg

プリプレグ ガラス繊維、炭素繊維などからできた織物に未硬化の樹脂を含浸した成型材料。

PPA

Power, performance, and area

PPAC

Power, performance, area, and cost

プリント基板

部品を実装するための基板。部品間を接続するための配線が基板表面と基板内部に形成されている。

PWB

Printed Wired Board

部品が実装される前の配線だけされたプリント基板

PCB

Printed Circuit Board

部品が実装された後のプリント基板

Q

QFN

Quad flat non-leaded

四角形の側面に入出力用の端子が規則正しく並んでいるパッケージ(リードはなし)

QFP

Quad flat package

四角形の側面に入出力用のリードが規則正しく並んでいるパッケージ

R

RDL / 再配線層

Re-Distribution Layer

チップの入出力パッドからパッケージの入出力パッドへと信号をやりとりする高密度な配線層

S

SA D2W

Self assembly die to wafer

SoC

System on Chip

1つの半導体チップ上に異なる機能を集積する技術。例えば、CPUと大容量Memory、高耐圧電源ICと低電圧CPU、などをワンチップ化。SoCの欠点は、高い歩留まりをKeepするのが困難であることと、製造工期が長い。

SoIC

System on Integrated Chips

tsmcのチップの積層技術。Hybrid bondingを用いたCu-Cu直接接合。

SoIS

System on Integrated Substrate

InFOデバイスに対して、更にFan-Outの配線層を形成。大型デバイス用。

SQB

Sequential bonding

each die is bonded completely before the next die is placed and bonded

SSDs

Solid-state drives

フラッシュメモリーを用いるドライブ装置

SiP

System in Package

複数の半導体チップを1つのパッケージ内に封止する技術。半導体Chipをそれぞれ作製し、実装プロセスで組み合わせる。SiPの欠点は、チップ間の配線を設けるため、SoCと比較して応答速度などで性能が低いこと。

再配線層 / RDL

チップの入出力パッドからパッケージの入出力パッドへと信号をやりとりする高密度な配線層

SMT / 表面実装

Surface Mount Technology

プリント基板の表面にデバイスを実装する方法

SLIM

SiliconーLess Integrated Module

AmkorのTSV Heterogeneous integration

SLIT

SiliconーLess Interconnect technology

AmkorのTSV less Heterogeneous integration

SWIFT

Silicon Wafer Integrated Fan-Out Technologhy

AmkorのTSV less Heterogeneous integration

S-connect

AmkorのBrigdeを使用したTSV less Heterogeneous integration

S-SWIFT

Substrate SWIFT

AmkorのTSV less Heterogeneous integration。SWIFT構造を基板に実装する。

T

TB

Temporary bonding

仮固定ウエハにチップを接着する工程

TBDB

Temporary bonding and debonding

仮固定ウエハにチップを接着、剥離する工程

TCB

Thermo compression bonding

熱処理によって仮固定ウエハにチップをBondingする工程

TGV

Through Glass Via

ガラス基板に垂直に形成されたVia。

TIM

Thermal inteface material

熱伝導性材料。パッケージ内の放熱を促す。

TIV

Through InFO Via

InFO PoPに使用されている、上下のパッケージを繋ぐためのモールド樹脂を貫通するVia。

TSV

Through Silicon Via

シリコン基板に垂直に形成されたVia。

U

V

VeCS

Vertical Conductive Structures

VCB

Vertical Collective Bonding

the first dies are picked, aligned and bonded at low temperature for a very short time.Only after attaching the last die, a complete TCB profile is applied to the multilayer stack.

W

WB

Wire bonding

信号の取り出し口がBumpではなく、Wireを用いた実装方法

WLCSP

Wafer Level Chip Size Package

ウエハプロセスで再配線層からダイシングまでを実施する工程

WLP

Wafer Level Package

ウエハのまま必要な再配線や封止、Bumpの搭載などを行い、個片化するプロセス

WoS

Wafer on Substrate

WoW

Wafer on Wafer

X

XDFOI

X-Dimensional Fan-Out Integration

J-CETのTSV less WLP technology

Y

Z

2

2D実装

チップとチップを配線基板で繋ぐ実装方法。

2.xD実装

チップと樹脂基板の間に配線基板を用いる実装方法。配線基板のことをインターポーザーと呼ぶ。

2.1D実装

2.xD実装で、インタポーザーに、有機基板を使った場合の呼称

2.3D実装

2.xD実装で、インタポーザーに、微細パターニングフィルム+有機基板を使った場合の呼称

2.5D実装

2.xD実装で、インタポーザーに、Si基板を使った場合の呼称

3

3D実装

チップ同士を積層した実装方法

実装技術の動画による解説はこちら

WLPの製造工程はこちら

InP(インジウムリン)はIII / V族半導体の一種であり、シリコンに比べて高い電子移動度と高い飽和電子速度を備えています。

バンドギャップが広く、高い動作周波数を有し、高周波デバイスに利用されています。

また、InPもGaAs同様、直接遷移型の半導体であり発光させることが可能です。InPで代表されるデバイスに端面発光レーザー(EEL)があります。光通信の分野で長く利用されてきており、主にパワーを必要とする長距離向けで使用されます。

このEELのプロセスフローの中には、100nm程度のグレーティングを形成後、MOCVDによるエピ膜の再成長を行う工程があります。グレーティング形成においては寸法精度とダメージレスが求められます。再成長膜は、その後、リッジ形成し、保護膜形成、電極付けという流れになります。なお、このリッジ形成については、近年、深掘り要求が増えており、ULVACではマスク選択比30以上で、非常に平滑な側壁と垂直性を得るエッチングプロセスを確立しています。

GaAs(ガリウム砒素)はIII / V族半導体の一種であり、シリコンに比べて高い電子移動度と高い飽和電子速度を備えています。

バンドギャップが広く、高い動作周波数で、シリコンデバイスよりもノイズが少なく、高周波デバイスとして多用されています。

また、間接遷移型の半導体であるシリコンとは異なり、GaAsは直接遷移型の半導体で発光させることが可能です。昨今、スマートフォンの顔認証用途に採用され、市場が拡大したVCSEL(面発光レーザー)はGaAs系の代表的な発光デバイスです。以前より光通信の短距離分野で長く利用されて来ており、その他、センシング、セキュリティー分野でも利用されています。

このVCSELのプロセスフローの中で、GaAs/AlGaAs多積層膜を任意の深さにエッチングしたいという要望もあり、ULVACでは、その制御が可能なプロセスを構築しています。

VCSELプロセスフロー

化合物半導体は電磁波の一種である光や電波を扱うために適した半導体です。

電子の移動度が、はるかに速いため、高速信号処理に優れ、マイクロ波やミリ波(5G)の増幅器(PA)に使用されます。古くはGaAs、現在はGaN-HEMTが5Gの携帯基地局に使われています。

また化合物半導体は発光素子として必須の材料で、元素の組合せで様々な波長をカバーします。赤外はInP、AlGaInP、AlGaAsといった組成となり、端面発光レーザー(EEL)や、面発光レーザー(VCSEL)に使われ、光通信、センシング、セキュリティーの分野で顔認証やLiDAR、自動運転といった用途で使用されます。

青、紫ではGaNが使用され、照明、ヘッドランプ、ディスプレイに利用されており、u-LEDは次世代ディスプレイとして注目されています。現在は緑、赤の波長への拡大も研究開発が進んでいます。

これらはXRの分野で融合し、メタバースの世界でも必要なデバイスになるでしょう。

なお、紫外はAlN、AlGaNといった組成となり、DUV(深紫外)は殺菌、浄水へ適用可能で、新型コロナを不活化できる波長として期待されています。

ちなみに、GaN、SiCは破壊電界強度が高いため、次世代パワー半導体としても期待されており、鉄道、EV、最近は急速充電器にも利用が拡大しています。