IGBTプロセスで必要となるイオン注入技術について紹介します。

P+,N+ Field Stop層形成

P+,N+ Field Stop層の形成には、プラズマ源IHCを使用しているイオン注入装置が使用されます。IHCはIndirect Heat Currentの略で、特徴は、フィラメントがDirectにプラズマ表面に晒されないので長寿命です。

原理はフィラメントから熱電子が放出され、それがカソードの衝突し、カソードから電子が放出され、リペラーで反射されながら電子が導入されたガスにぶつかりプラズマを形成していきます。

ULVACのイオン注入装置SOPHI-400で本機構を採用しております。

IGBTの製造工手の中で、電極形成に必要となるスパッタリングの技術について紹介します。

スパッタリング(電極形成)

IGBTの電極形成に使用される薄ウェーハ対応スパッタリング装置は量産工場で数多く使用されています。薄ウェーハの割れを回避するためのNi 又はNiV成膜による応力コントロールをする技術が重要です。

例えば、特殊冷却ステージを使用し温度制御するという方法があります。原理はPure Ni成膜中、低温で成膜することにより、応力を軽減させることで実現します。また、NiVのX Parameterを使うことによりNiVの応力コントロールも可能です。

ULVACのスパッタリング装置はuGmniは、これらの技術が使われており300mm の薄ウェーハ対応装置も提供しています。

枚葉式複合モジュール型成膜加工装置uGmniについて

枚葉式複合モジュール型成膜加工装置uGmniは、スパッタリング、エッチングなど複数の異なるプロセスモジュールを同一搬送コアに搭載し、可能な限り構成部品の共通化を行い、スペア部品の低減や同一操作画面による使い勝手向上など、電子部品の製造工程において更なる効率化を実現いたします。

メンテナンス性にも優れております。

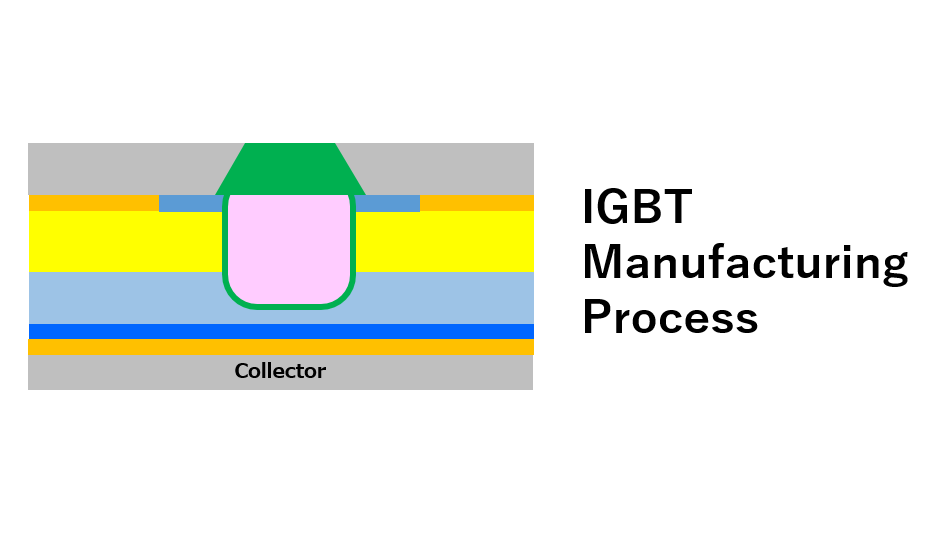

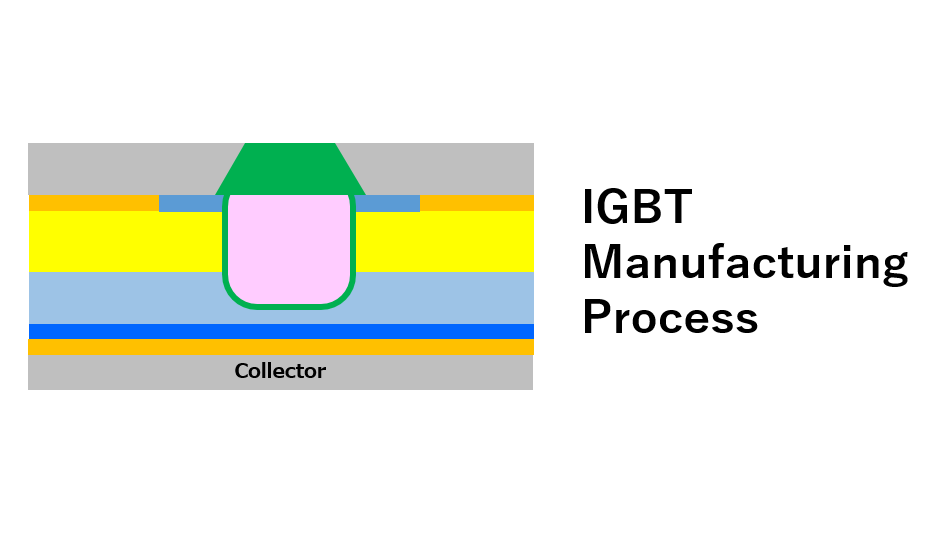

ULVACではパワーデバイスIGBTの製造プロセスに向けたイオン注入装置、スパッタリング装置 等の技術を提供しています。パワーデバイスIGBT(絶縁ゲート型バイポーラトランジスタ)とはInsulated Gate Bipolar Transistorの頭文字を取ったものです。

パワーデバイスIGBTのプロセスフロー

1.基板

2.B+注入

イオン注入装置を使用します。

3.マスク用絶縁膜形成

CVDでマスク形成をします。

CVD装置の紹介

4.マスク用絶縁膜加工

エッチングとアッシングで絶縁膜を加工します。

5.P+注入

イオン注入装置を使用します。

6.トレンチ形成

エッチングでトレンチを形成します。

ドライエッチング装置の紹介

7.絶縁膜形成

CVDで絶縁膜を形成します。

CVD装置の紹介

8.絶縁膜加工

エッチングとアッシングで絶縁膜を加工します。

9.Emitter電極形成

スパッタリングや蒸着で電極形成をします。

スパッタリング装置の紹介

10.P+ FS層形成

イオン注入装置でP+FS層を形成します。

イオン注入装置の紹介

11.B+(Collector)形成

イオン注入装置でB+(Collector)を形成します。

IGBT向け加工技術の紹介(イオン注入)

イオン注入装置の紹介

12.Collector形成

スパッタリングや蒸着でCollector形成します。

IGBT向け加工技術の紹介(スパッタリング)

スパッタリング装置の紹介

ULVACのキーテクノロジー

Ion Implantation

・FS層向けリン注入によりIGBT性能向上

・FS層向け水素注入によるCost低減

Sputtering

・薄ウエハー搬送可能

・応力調整

Etching

・Trench構造にも対応

PE-CVD

・27MHz駆動の低Damage Plasma

・基板Biasによる膜応力controlも可能

システムインパッケージ(SiP)とは複数の半導体チップを1つのパッケージ内に封止する技術ことです。半導体Chipをそれぞれ作製し、実装プロセスで組み合わせます。

対してシステムオンパッケージ(SoC)は1つの半導体チップ上に異なる機能を集積する技術です。例えば、CPUと大容量メモリ、高耐圧電源ICと低電圧CPU、などをワンチップ化する技術のことをいいます。

SiPは、チップ間の配線を設けるため、SoCと比較して応答速度などで性能が低いこと。SoCは、高い歩留まりをKeepするのが困難であることと、製造工期が長いなどそれぞれ違いがあります。

再配線層、Build up配線以外にも、SiP向けにプラズマ技術は応用されています。 この動画ではULVACが提供する表面改質処理といったアプリケーションを紹介します。

アッシング装置紹介はこちら

実装工程プロセスの紹介はこちら

お問い合わせはこちら

Printed Circuit Board (PCB)とは絶縁体の内部、または、表面に金属配線が施された電子部品が取り付けらる基板のことです。半導体パッケージ(実装)製品の王道製品と言えます。 アルバックは、PCB製品の微細化技術に一役買っています。 将来をターゲットに据えたドライ化技術について紹介します。

アッシング装置紹介はこちら

実装工程プロセスの紹介はこちら

お問い合わせはこちら

最先端のパッケージ(実装)製品には、プラズマ技術が既に使われています。アルバックではウェハー、パネル向けのプラズマアッシング装置を提供しています。これらのアッシング装置はバッチ式ではなくアッシングレートの面内分布を意識した枚葉式の装置です。

一般的にアッシングとは、フォトレジストをプラズマで分解し除去する工程です。アルバックでは実装の工程のアッシングは比較的簡単なエッチングをするという意味合いで使われています。

アッシング装置紹介はこちら

実装工程プロセスの紹介はこちら

お問い合わせはこちら

半導体パッケージ(実装)製品のトレンドと言えば、ファンアウト(Fan-out)。アルバックはファンアウトパッケージの量産化技術に貢献しています。 ここでは、プロセスフローとプラズマ技術についてご紹介します。

Key word

Fan-Out(FO) : チップに対して扇状に配線を広げた構造。

Package on Package (PoP) : パッケージを積層した構造。

Redistributed layer (RDL)、再配線層 : チップと外部取り出し部までの配線層

Descum : フォトリソグラフィー後の残渣を除去する工程

感光性樹脂 : 光を照射することで性質が変化する高分子材料の総称。

Polyimide : Imide結合を含む高分子化合物の総称。

アッシング装置紹介はこちら

実装工程プロセスの紹介はこちら

お問い合わせはこちら

プラズマ発生方法は、沢山種類があります。その中で、アルバックはパッケージ(実装)製品に適したプラズマ源を採用しています。主に下記の放電方式があります。

Surface Wave Plasma (SWP) : マイクロ波の表面波によって誘電体透過窓表面に表面波を生成。この表面波によって、透過窓付近にプラズマを発生する方法。

Capacitively Coupled Plasma (CCP) : 2枚の金属電極に片方に高周波電源が接続されており、 極板間の電場形成によってプラズマを発生する方法。

Dual frequency Capacitively Couple Plasma (2-Freq CCP) :2枚の電極基板それぞれに異なる高周波電源が接続されているCCP方式。

アッシング装置紹介はこちら

実装工程プロセスの紹介はこちら

お問い合わせはこちら

半導体チップの微細化が難しくなっている中、デバイスの性能を高めるためにパッケージ技術が注目を集めています。異種デバイスを集積し、高性能化する技術を「More than Moore」といい複数の半導体パッケージを一つの半導体パッケージに封止する技術をシステムインパッケージといいます。

アルバックは半導体パッケージ(実装)の量産化技術の開発に力を入れています。ここでは、パッケージ(実装)向けプラズマ技術の背景をご紹介します。

アッシング装置紹介はこちら

実装工程プロセスの紹介はこちら

お問い合わせはこちら