アルバックは、2026年度も引き続き大阪大学と博士人材育成に取り組みます。 このプロジェクトは、大学と企業が協力し、未来を担う研究者を育てることを目的としています。私たちは、産学連携を通じて社会に新しい価値を生み出すことを目指しています。

活動のポイント

この取り組みの中心となるのは、大阪大学の「未来基金」への寄付です。これにより、研究と教育の両面で連携を強化しています。大学の最先端研究と、アルバックが長年培ってきた産業技術を組み合わせることで、社会課題を解決し、新しい価値を創出することを目指しています。こうした協力関係は、単なる資金提供にとどまらず、知識と技術の融合によるイノベーションを促進します。

なぜ博士人材育成が重要なの?

博士課程の学生や研究者には、深い専門知識だけでなく、産業界で求められる実践的な課題解決力が必要です。このプロジェクトでは、学術と産業をつなぐ次世代の人材を育成することをめざしています。産業界で活躍できる博士人材を育てることは、日本の技術力強化にもつながります。

これまでの成果

これまでに、多くの博士課程の学生が学会や国際会議で成果を発表しました。さらに、共同研究から新しい研究テーマが生まれ、外部資金の獲得にもつながっています。 こうした成果は、大学と企業の双方にメリットをもたらし、「双方向型の共創モデル」として定着しつつあります。このモデルは、研究と産業の距離を縮め、イノベーションを加速させる重要な仕組みとなっています。

これからどうなる?

2026年度は、これまでの成果をさらに発展させ、博士人材育成とオープンイノベーションを両立させる取り組みを続けます。未来基金を通じた支援により、産学連携をさらに深め、社会に貢献する研究を推進します。 興味のある方は、大阪大学の未来基金サイトもぜひチェックしてみてください!

関連外部サイト

大阪大学の未来基金について

https://www.miraikikin.osaka-u.ac.jp/greeting

大阪大学未来基金 「産学官共創による工学博士人材育成事業」

「つながる・ひろがる 真空の輪」をカタチにした一日!

~4,500名が参加!~

2025年11月15日(土)、アルバック茅ヶ崎本社・工場にて「ULVAC Festival 2025(ULFes2025)」が開催されました! 今年のテーマは「つながる・ひろがる 真空の輪」。秋晴れの空の下、地域の皆さまや来場者の方々にご参加いただき、笑顔あふれる一日となりました。

「真空の世界にふれてみよう!」体験型イベントが充実

屋内では、アルバックの技術を楽しく学べる体験型コンテンツが盛りだくさん!

未来技術研究所 × 大阪大学の協働研究紹介

分析室見学ツアー

半導体製造プロセスをゲーム感覚で体験できるデジタルコンテンツ

昨年好評だった「真空実験」や「クリーンルーム入室体験」も継続開催。子どもたちが目を輝かせながら参加する姿が印象的でした。

海外グループ会社による「海外文化体験」では、各地域の遊びや文化を通じて国際交流も楽しめました。

中庭では、森林プロジェクトとビーチクリーン活動がコラボした「オリジナルフォトフレーム製作体験」も開催。自然素材を使ったクラフトに親子で夢中になる姿も見られました。

食欲の秋を満喫!飲食ブースが大盛況

お祭りの楽しみといえばグルメ。今年も「たこ焼き」や「ちょぼ焼き」の屋台が登場し、香ばしい匂いに誘われて長蛇の列が。アルバックの東北・九州工場から届いた焼酎や日本酒も好評で、大人にも人気でした。

茅ヶ崎市近隣の飲食店によるキッチンカーも多数出店し、子どもから大人まで満足できるラインナップで"食欲の秋"を堪能できるフェスとなりました。

さいごに

「つながる・ひろがる 真空の輪」をテーマに開催された ULFes2025。技術と地域、そして未来への想いが交差する、あたたかく楽しい一日となりました。

アンケートでは、半数以上が初めての参加で、満足度は9割を超えることができました。ご来場いただいた皆さま、そして運営にご協力いただいたすべての方々に心より感謝申し上げます。

来年も、さらに進化した ULFes でお会いしましょう!

2025年9月29日、韓国の大手半導体メーカーSK hynixが開催した「Partners Day」で、アルバックが「Best Partner Award」を受賞しました。この表彰は、SK hynixの半導体製造工程において、アルバックのスパッタリング装置「ENTRON」が正式採用(POR)され、その高い技術力と品質向上への取り組みが評価されたものです。

評価された3つのポイント

1.技術信頼性の確保 スパッタリング装置「ENTRON」が、SK hynixの製造工程で求められる高い信頼性を実証しました。 均一な膜品質を安定して提供できることが認められ、POR(Process of Record)を獲得しました。2.グループ連携による技術力強化 アルバックグループ全体で、開発から性能検証、顧客対応までを一体となって推進しました。 日本と韓国のチームが緊密に連携し、課題解決に取り組んだことが評価されています。3.事前評価体制の整備 韓国・平澤にあるTechnology Center PYEONGTAEKに評価システムと検証プロセスを導入し、開発初期から 品質の安定性を確保しました。この体制により、顧客の要求に迅速かつ確実に応えることが可能になりました。

社長コメント

ULVAC KOREA, Ltd.の崔承洙(チェ・スンス)社長: 「新しい市場や技術への挑戦は決して簡単ではありません。しかし、諦めず挑戦し続ける姿勢こそが最も大切です。今回の成果は、私たちの努力と情熱が一つになった結果です。過去20年間、幾度もの困難を乗り越えてきた当社にとって、SK hynix向けプロジェクトの成功は大きな意味を持ちます。今後も挑戦と協力の精神を大切にし、さらなる飛躍を目指します。」

PORとは?

半導体製造において、特定の装置や材料が正式に採用されるプロセスのことです。PORを獲得することは、技術信頼性の証であり、メーカーにとって重要なマイルストーンです。

アルバックの今後

今回の受賞を機に、アルバックは顧客との共同開発をさらに強化し、半導体市場での技術基盤を確立していきます。

2025年11月3日、ULVACとULVAC KOREAは、Samsung Electronics Co., Ltd.(以下、Samsung)が開催した「Appreciation Day 2025」において、「功労賞」を受賞しました。

この賞は、長年にわたるSamsungとの強いパートナーシップが評価されたものです。 私たちは、半導体製造に欠かせない装置に関する技術サポートや、 安定した供給体制の構築に継続的に取り組んできました。 その結果、製品の品質および生産性の向上に貢献できたことを誇りに思います。

2025年9月12日、台湾の大手ディスプレイメーカー AU Optronics Corporation(以下、AUO)が開催した 「2025 AUO Global Partner Summit」で、アルバックが 「Excellent Equipment Partners Award」を受賞しました。

この国際的なイベントは、AUOが2〜3年に一度開催するパートナー会議で、 今年は「Together, Unlimited Possibilities(共に、無限の可能性を)」をテーマに、 北米・欧州・アジア太平洋地域から116社、300名以上の主要取引先が参加しました。 会議では、AUOの経営方針や持続可能な成長に向けたビジョンが共有されました。

受賞理由

アルバックは、装置の性能要件を満たすだけでなく、以下の取り組みが高く評価されました。

納期への柔軟な対応 生産計画に合わせた迅速な対応で、AUOの安定供給に貢献しました。

技術サポートの強化 導入後の技術支援や課題解決に積極的に取り組みました。

長年の協力関係 アルバックのVMS BUとアルバック台湾(UTI)は、20年以上にわたりAUOと協力し、 設備だけでなく技術やサービスの面でも生産を支えてきました。

こうした取り組みが、AUOにとってアルバックが「重要な成長・協業パートナー」であることを改めて示しました。 今回の受賞盾は、工業素材の「コンクリート」と自然素材の「木」を融合したデザインで、 異なる要素の調和を象徴しています。このデザインには、「共に未来を切り開く」という思いが込められています。

今後の展望

今回の表彰は、AUOの強い信頼を示すものです。アルバックは、これからも技術力とサービスをさらに高め、 グローバル市場での共創を進めていきます。

右から2人目がULVAC TAIWAN 呉総経理、中央がAUO Supply Chain総部 Ken陳資深経理

写真左から2人目:AUO Frank柯富仁総経理、3人目:ULVAC TAIWAN 呉総経理、4人目:AUO Paul彭雙浪董事長兼会長、6人目:AUO Supply Chain総部 Ken陳資深協理

韓国から、ULVACにとって大変嬉しいニュースが届きました!

2025年10月22日、ソウルのグランドインターコンチネンタルパルナスで開催された「半導体の日」記念式典において、ULVAC KOREA, Ltd. の白忠烈顧問(元アルバック取締役)が韓国政府より「産業褒章」を受章しました。

この褒章は、韓国の産業発展に大きく貢献した個人・企業に授与される栄誉ある賞で、白忠烈氏は長年にわたり半導体製造装置の技術開発や産業競争力の向上に尽力してきた功績が高く評価されました。今回の受章は、アルバック創業メンバー以外では初めて、さらに海外グループ会社のメンバーとしても初の快挙となります。

「半導体の日」は、韓国の半導体産業の発展に寄与した個人・団体をたたえるイベントで、今年で18回目を迎えました。当日は約550名の業界関係者が出席し、盛大に開催されました。

白忠烈氏から、次のようなコメントをいただきました:「韓国でのアルバックのモノづくりとお客様への貢献が認められたことを嬉しく思います。これからもアルバックの半導体事業のさらなる成長を願っています。」

今回の受章は、ULVACグループ全体にとっても大きな意味を持つ出来事です。これからも技術革新を通じて、産業の発展に貢献していきます。

写真向かって左端:ULVAC KOREA 金鍾大専務

ULVAC KOREA, Ltd.の金鍾大専務が「産業通商資源部長官表彰」を受賞しました!

2025年9月26日、韓国で開催された「第16回ディスプレイの日」記念式典で、ULVAC KOREA, Ltd.の金鍾大(Jong-Dae Kim)専務が、韓国産業通商資源部から「産業通商資源部長官表彰」を受けました。「ディスプレイの日」は、韓国のディスプレイ産業を支える企業や研究者をたたえる特別な日。

今年で16回目を迎えたこの式典では、技術革新や国際競争力の向上に大きく貢献した人々が表彰されます。金専務は、スパッタリング装置の改良や改善をリードし、主要顧客の生産性向上に大きく貢献してきました。その功績が認められ、今回の受賞につながりました。

受賞にあたり、金専務はこう語っています。「この賞は私一人のものではなく、アルバックのVMS BU(Business Unit)の仲間全員の努力の結果です。アルバックの成長に貢献できたことを誇りに思います。」

今回の受賞は、アルバックグループ全体が技術革新と産業発展に貢献していることを示す大きな成果です。

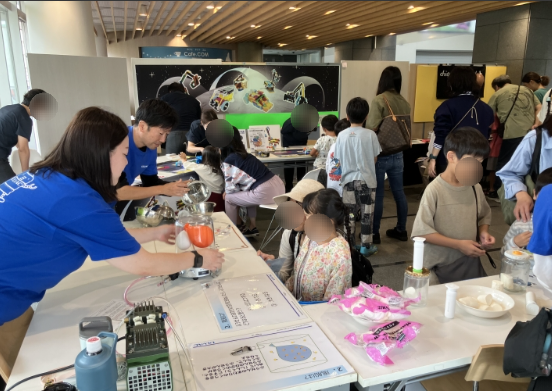

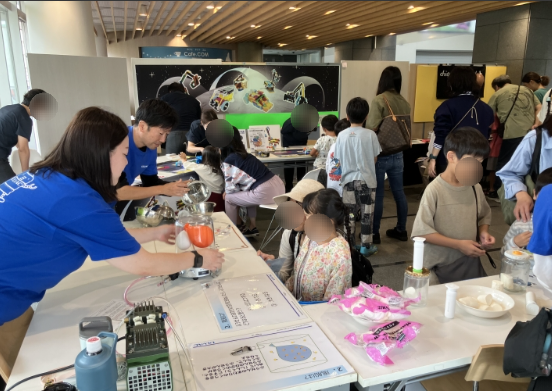

2025年10月13日、茅ヶ崎市役所で開催された「第2回青少年フェスティバル 子どもふれあいまつり」に参加しました!

今年で2回目となるこのイベントは、「日本宇宙少年団茅ケ崎分団」や「ちがさき宇宙フォーラム」などが中心となって運営されており、 子どもたちがのびのびと交流できる新しい形のフェスティバルとして企画されています。

会場となった茅ヶ崎市役所の庁舎内では、ダンスやチアリーディング、一輪車、縄跳びなど、 元気いっぱいのパフォーマンスが次々と披露され、たくさんの観客でにぎわいました。

私たち ULVAC(アルバック) も、昨年に続き「真空実験ブース」を出展! 子どもたちが目を輝かせながら実験に参加する姿に、スタッフ一同とても嬉しくなりました。

実は、日本宇宙少年団茅ケ崎分団の初代団長は、当社の第3代社長・林主税氏。 そんなご縁もあり、私たちはこのイベントを大切にしています。

来場者の中には、「先日サッカーの試合でグラウンドをお借りしました。また来月もアルバックに行きます」と 声をかけてくださる親子や、「ULVAC Festivalのポスター見ました!楽しみにしています!」と話してくださる地域の方もいて、 地域とのつながりを改めて感じる一日となりました。

今後も、教育委員会と連携しながら青少年の育成に貢献し、地域との絆を深めていきたいと考えています。

富士裾野工場、使用電力を実質すべて再生可能エネルギーに!

2025年7月から、当社の富士裾野工場で使う電気が、実質的にすべて再生可能エネルギー(再エネ)由来のものになりました。

再生可能エネルギーとは、太陽光や風力など、自然の力を使って作られる電気のこと。環境にやさしく、地球温暖化の原因となるCO2の排出を減らすことができます。

どうやって実現したの?

今回の切り替えは、東京電力エナジーパートナー株式会社が提供する「オフサイトコーポレートPPA」という仕組みを使っています。これは、工場の敷地外にある太陽光発電所で作られた電気を、一般の電力網を通じて工場に届ける契約のことです。

この仕組みを使うことで、年間約3,200メガワット時(MWh)もの再エネ電力を安定的に調達でき、約1,300トンものCO2排出を減らすことが見込まれています。

さらに、再エネ電力証書という環境価値の証明書も購入しているため、富士裾野工場で使う電気は「実質的に100%再生可能エネルギー由来」と言えるのです。

再生可能エネルギーのメリットって?

環境にやさしいCO2の排出を減らし、地球温暖化の防止に貢献します。

電気代の安定再エネは価格が安定しているため、電気代の急な高騰リスクを減らせます。

企業価値の向上環境に配慮した取り組みは、社会からの信頼や評価を高めます。

今後の取り組み

当社は、2030年までに温室効果ガス排出量を2023年比で50%削減し、2050年には実質ゼロを目指しています。富士裾野工場だけでなく、九州工場でも太陽光発電設備を稼働させるなど、国内外で再生可能エネルギーの導入を計画的に進めています。

これからも持続可能な社会の実現に向けて、環境にやさしいエネルギーの活用を推進していきます。

用語解説

オフサイトコーポレートPPA

工場の敷地外にある再生可能エネルギー発電所から電気を購入し、一般の電力網を通じて供給を受ける契約のこと。 敷地内に発電設備を設置するよりも多くの再エネを安定的に調達できます。

再エネ電力証書

電気そのものとは別に、再生可能エネルギーで作られた電気の環境価値を証明する証書のこと。 これを購入することで、実質的に再エネ由来の電力を使っていると認められます。

これからもアルバックは、環境にやさしい技術と取り組みを通じて、みなさまと一緒に持続可能な未来をつくっていきます。

応援よろしくお願いします!