電気二重層キャパシタ(EDLC)は高出力と長寿命に優れた蓄電デバイスであるが,エネルギー密度が低いという課題がある。近年では温室効果ガスの排出量削減に関して世界的に政策が進められており,ハイブリット自動車(HEV)や電気自動車(EV)などに搭載するためのキャパシタにも高エネルギー密度化が求められている

そのため, Fig.1 に示すような活性炭を正負極に用いたEDLC の負極側をリチウムイオンがドープ可能な材料に置き換えることで,エネルギー密度を向上させたリチウムイオンキャパシタ(LIC)1, 2)の開発も盛んに行われるようになってきたFig.2 に各種蓄電デバイスのラゴンプロットを示す3)。ラゴンプロットとは横軸に出力密度(瞬発力に相当),縦軸にエネルギー密度(持久力に相当)を示したものである。理想的にはラゴンプロットの右上に位置する特性を持つことが望ましく,LIC はEDLC の瞬発力とリチウムイオンバッテリー(LIB)の持久力をどちらも兼ね備えた理想の蓄電デバイスとしての可能性を秘めている。

EDLC はその高出力特性から自動車の回生エネルギーシステムや,中国国内の路面電車,路線バスなどにも既に普及している4)。大電流で一気に充電を行うことで次の停留所や駅までの決められた短距離間を走行することができる。この蓄電池の部分をLIC で置き換えることにより,大量に積載しているEDLC を小型・軽量化でき,航続距離の改善も可能となる。将来的には急速充放電が可能になり,一般道路にもワイヤレス給電の技術が普及することで,LIC 単独のEV が実現することにも期待できる。我々がLIC の評価を開始した背景として,これまでリチウム- 硫黄二次電池(LiS)と呼ばれる次世代二次電池の正極材料に,化学気相成長(Chemical Vapor Deposition: CVD)法で作製したカーボンナノチューブ(CNT)電極の開発を行ってきたことが挙げられる。

この電池の課題として,硫黄が絶縁物であるため多量の導電材が必要となることが挙げられる。アセチレンブラックなどの炭素材料より導電性に優れたCNT を用いることで導電材の割合を減らすことが可能となり,電池特性向上につながる。熱CVD 法で作製されたCNT はニッケル金属箔上から垂直に配向しており,電極上部まで良好な電子伝導パスが形成されている(Fig.3 を参照)ため,硫黄の充填量を飛躍的に向上させることが可能であることをこれまで確認してきた5)。

本稿では,この導電性に優れた垂直配向CNT 電極がLIC の負極材料としても適用できるかどうか検証した結果について紹介する。

(※この記事は、2019年9月発行のテクニカルジャーナルMo.83に掲載されたものです。)

記事の続きは下記URLよりアルバックテクニカルジャーナルにユーザ登録するとご覧いただけます。https://www.ulvac.co.jp/research_development/technical_journal/index.htmlhttps://www.ulvac.co.jp/r_d/technical_journal/tj83j/

文献1) M. Morita: Electrochemistry 85, 736(2017).2) T. Chiba: Electrochemistry 85, 796(2017).3) https://www.jmenergy.co.jp/lithium_ion_capacitor/.4) "キャパシタ技術"平成30年度第3回研究会特別号, 28(2018).5) Y. Fukuda: The 19th International Meeting on Lithium Batteries(2018)803.

本研究は,文部科学省『省エネルギー社会の実現に資する次世代半導体研究開発』事業JPJ005357ににおける名古屋大学殿の協力機関としての成果が含まれる。本事業では,次世代半導体材料として有望な窒化ガリウム(GaN)に関して,材料創製からデバイス動作検証・システム応用までの研究開発を一体的に行う研究開発拠点を構築し,理論・シミュレーションも活用した基礎基盤研究を実施することにより,実用化に向けた研究開発を加速することを目的としている。

GaNパワーデバイスの低ダメージドライエッチング技術

近年の飛躍的な科学技術の進歩に伴い,エネルギー消費量は世界的にますます膨大になっている。一方で,エネルギー発電やガソリン自動車等から排出される二酸化炭素(CO2)や温室効果ガスが環境に与える影響は甚大であり,地球温暖化防止,省エネルギー化を目指した研究開発がとても重要になっており,喫緊の課題である。

GaNは,現在半導体パワーデバイスの主流となっているシリコン(Si)に比べて,バンドギャップエネルギー及び絶縁破壊電界強度が大きく,また電子移動度が高く,優れた基礎物性を有している。そのため,GaNは低損失かつ高耐圧パワーデバイスとして,特に環境負荷軽減となるハイブリッド電気自動車(HV)や電気自動車(EV)への応用が期待されている。

GaNを用いたパワーデバイスには,様々な素子構造の研究開発が進められている1 )。その中でも,デバイス構造の特徴から縦型トレンチゲートMetal-oxidesemiconductor field-effect transistors( MOSFETs)は,チップの小型化と高速スイッチングを可能にするデバイスとして注目されている。トレンチゲートという名称の通り,GaNウェーハ表面に,幅・深さが1 μm程度の溝(トレンチ)を形成することで,デバイスのオンオフのスイッチング動作を行うゲートとして機能させる。

トレンチは,エッチング工程により形成される。その側壁はデバイス動作時に反転層として電子が流れる経路となる。そのため,垂直性及び側壁表面の平坦性が良好なトレンチを形成するエッチング技術は,特にチャネル移動度というデバイス評価指標を向上させるための必須の技術となる。また,トレンチ形成の際に導入されるGaNへのダメージの低減も重要な課題である。

本報告では,GaNトレンチ形状制御と低ダメージ化に向けた最近のアルバックの取り組みと得られた成果を紹介する。

(※この記事は、2021年4月発行のテクニカルジャーナルMo.84に掲載されたものです。)

記事の続きは下記URLよりアルバックテクニカルジャーナルに

ユーザ登録するとご覧いただけます。

https://www.ulvac.co.jp/r_d/technical_journal/tj84j/

文 献

1) T. Kachi: Jpn. J. Appl. Phys. 53, 100210( 2014).

光学多層膜はガラスや樹脂,金属などの基材に数種類の屈折率の異なる材料を交互に形成することで特定波長の光を透過・反射する機能をもたせた薄膜である(Fig.1)。かねてよりレンズの反射防止膜や増反射ミラーなどで使用され,光学フィルタやハーフミラーなど応用例は多岐にわたる。

光学薄膜の原理

また,近年では3D顔認証用のセンサー,距離計測用のLiDAR(Light Detection and Ranging),生体認証などのデバイスにも光学薄膜が活用されている。これらのデバイスではFig.2に示すように,光源から特定の波長の光を対象物に照射し,対象物から反射してきた特定波長の光のみを検出するため,BPF(Band Pass Filter)が用いられている。特に,顔認証用途の近赤外BPFは,広い視野角にわたって信号損失を少なくするため,対象物からの反射光が大きな角度で入射した場合でもBPF透過帯の中心波長のオフセット量が小さく,高透過率のものが求められる。

BPF(バンドパスフィルター)の原理

そのため,これまで主に使用されてきた高屈折率成膜材料のTa 2 O 5 ,Nb 2 O 5,TiO 2に比べて,近赤外波長領域での屈折率が高く可視光波長領域を吸収する特性をもつ水素化アモルファスシリコン(a-Si:H)を使用したBPFが注目されている1 )。a-Si:Hを使用することでBPFの膜層数,膜厚の低減が可能となり生産性の向上が期待される。

また,Fig.3に示すようにスマートフォンのカメラモジュールなどは,従来レンズや光学フィルタなどの光学部品とCMOSなどの半導体部品を別々に製造後,モジュールとして組み立てを行っていたが,今後ウェーハレベルで各部品を作製,貼り付けを行った後にカットするWLO(Wafer Level Optics)と呼ばれる製造方法が主流になると言われている。そのため,φ200 mm,φ300 mm ウェーハへの対応,品質面においても従来より低パーティクル装置・ハンドリング管理の対応が求められる。光学膜の成膜方法としては蒸着が用いられてきたが,光学膜の用途が広がるにつれ膜厚制御性や面内分布の要求がより高度になり,スパッタ法による光学膜の成膜に注目が集まっている。

光学デバイスの製造プロセス

記事の続きは下記URLよりアルバックテクニカルジャーナルに

ユーザ登録するとご覧いただけます。

https://www.ulvac.co.jp/r_d/technical_journal/tj84j/

半導体パッケージ(実装)分野でよく使われる略語/用語の一覧です。

単語

正式名称

内容

A

ABF

Ajinmoto build-up film

味の素ファインテクノ製のBuild-up film。業界シェアが100%に近い。

AM

Acoustic Microscopy

超音波顕微鏡

AiP

Antenna in Package

アンテナとRF chipを同一に実装する方法

AP / アプリケーションプロセッサー

Application processor

通信通話以外のオペレーション以外の動作を行うデバイス

アクセラレータ

サーバーの処理能力を向上させるツール

B

BEOL

Back end of line

半導体チップに配線を形成する工程

BGA

Ball grid array

パッケージ裏面にSolder bumpを格子状に規則的に並べた構造

Bridge

微細パターンが形成されたSi bridgeによって、ChipとChipを接続した実装方法。Si interposerをLocalに導入した実装方法。

Build-up配線

Build-up配線を用いた配線。基板の配線層に用いられる。

Build-up film

Build-up配線に用いられるフィルムで、樹脂とシリカフィラーの混合材料からできている。

C

カーボンニュートラル

温室効果ガスの「排出量」から、植林などによる「吸収量」を差し引いて、合計を実質的に"ゼロ"にすること。

Cavity flame core

PoPの上側と下側を繋ぐMetal配線が形成された積層基板 Samsungの技術

CCD

core complex die

CCD

CPU compute die

CF

Chip first

Fan-Out工程で、Chipを先にMountし、後でRDLを作製する方法

Cube

Samsungの2.5D実装の呼称

Chip First

Fan-Outで、チップを先に仮固定ウエハして再配線を形成する手法

Chip Last

Fan-Outで、再配線層を先に形成して、チップを固定する手法

Chiplet

半導体チップをそれぞれ製造して、後から配線ロスが極力減るように組み合わせる技術

CL

Chip last

Fan-Out工程で、RDLを先に形成し、後でChipをMountする方法

CMOS

complementary metal oxide semiconductor

Co D2W

Collective die to wafer

CoW

Chip on Wafer

CoWoS

Chip on Wafer on Substrate

tsmcの2.xD実装技術の呼称

CoWoS-S

tsmcの2.5D実装技術の呼称 Si interposerを使用。

CoWoS-R

tsmcの2.1D実装技術の呼称 Organic interposerを使用。

CoWoS-L

tsmcのBridgeを用いて2.xD実装 Local Si bridgeを使用。

COP

Co-packaged Optics

フォトニクス装置と電子スイッチを1つのパッケージにまとめ、信号の高速化や消費量削減や熱効率低減を目的としたパッケージ技術

CPU

central processing unit

周辺機器などからデータを受け取り制御・演算を実施するデバイス

CSP

Chip Size Package

半導体チップの大きさと同等レベルのパッケージ

D

データセンター

サーバーやネットワーク機器を設置するために特化した建物

DB

Debonding

基板接着されたチップ、または、接合されたウエハから、チップまたはウエハを剥離すること

DBG

Dice before grind

DBHi

direct bonded heterogeneous integration

IBMのBridge構造 ChipにBridgeを先に接続し、基板へ搭載

DBI

direct bond interconnect

Descum

フォトリソ工程後の残渣をScumと呼び、除去する工程をDescumという。

Desmear

レーザードリル工程後の残渣をSmearと呼び、除去する工程をDesmearという。

DTC

Decoupling capacitor

再配線層のノイズを目的としたSi Viaに形成されたCapacitor。

DP D2W

Dilect placement die to wafer

E

ECD

Electrochemical deposition

電界めっき工程

EFB

Elevated Fan-Out Bridge

AMDのFan-OutとBridgeを組み合わせた実装構造

EFI

embedded fine interconnect

IMEのBridge構造

EMIB

Embedded Multi-Die Interconnect Connect Bridge

IntelのBridgeを用いた実装方法。基板にBridgeを埋め込み、その後チップの搭載を行う。

F

Fabless

自社で製造ラインを持たず、FoundryまたはOSATに生産委託しているメーカー

Face up

Fan-Outの工程で、Padを上向きに搭載し実装する方法 InFOはChip firstのFace up工法

Face down

Fan-Outの工程で、Padを下向きに搭載し実装する方法

FAB

Fast atom beam

高速電子ビーム

FCBGA

Flip chip ball grid array

Flip chipを用いたBGA

FEOL

Front end of line

半導体チップのウエハ上に素子を形成する工程

FI

Fan-In

WLPの別名。Fan-Outに対する呼び方。

FO

Fan-Out

半導体チップに対して、取り出し口が広がっている構造。チップに対してBump数を増加することができる。

FOCoS

Fan-Out Chip on Substrate

ASEのTSV less Heterogeneous integration

FOEB

Fan-Out Embedded Bridge

SPILのBridgeを用いたFan-Out製品。

FOD

Film over die

FOPoP

Fan-Out Package on Package

Fan-Outのパッケージの上に異なるデバイスを搭載すること。

Foverous

Intelのチップの積層技術

Foverous-Omni

Intelのチップの積層技術 はんだBump-はんだBump

Foverous-Direct

Intelのチップの積層技術 Cu-Cu

Foundry

半導体チップの製造を請け負うメーカー

FC

Flip chip

半導体チップを切り出して、反転(Flip)して実装する方法

G

GAFA

米国のIT関連企業大手4社の頭文字をとった造語 Google, Apple, Face book, Amazon

GPU

graphic processing unit

画像処理に特化した演算を実施するデバイス

GX

グリーントランスフォーメーション

太陽光発電や風力発電といったグリーンエネルギーへの転換により、産業構造や社会経済を変革し、成長につなげること

H

Homogeneous integration

同種のチップを同一配線層で接続する実装方法

Heterogeneous integration

異種のチップを同一配線層で接続する実装方法

HAZ

heat affected zone

HDI

High density interconnect

HPMJ

high-pressure microjet

HPC

High performance computing

HBM

High Bandwidth Memory

DRAMが積層されたメモリー

HMC

Hybrid memory cube

Hybrid bonding

Bumpレス直接接合技術。Cu-Cuと絶縁膜-絶縁膜の直接接合。

Hybrid bonding Collective

仮固定ウエハを用いたHybrid bonding / アライナーで位置合わせする。

Hybrid bonding Suquential

Die bonderを用いたHybrid bonding

I

IDM

Integrated Device Manufacturer

設計・製造・組み立て・検査・販売を一貫して自社で行えるデバイスメーカー

IMT / 挿入実装

Insertion Mount Technology

プリント基板の内部にデバイスを実装する方法

I/O

Input / Output

Interposer

2.xD実装で使われるシリコンダイと樹脂基板間の配線基板

InFO

Integrated Fan-Out

tsmcのFan-Out技術の呼称

InFO oS

InFO (assembly) on Substrate

複数のChipをRDLで並列に繋ぎ、基板へ接続するInFO製品。

InFO B

InFO PoPの下側だけの状態。OSATの方で、上側のデバイスを接続する。

i-THOP

integrated Thin film High density Organic Package

新光電気の2.3Dパッケージ基板 アイソップ

J

JIEP

実装エレクトロニクス実装学会

K

L

LAB

Laser Assisted Bonding

レーザーによってチップまたはウエハを基板に接着する工程

LAL

light absorber layer

LDB

Laser debonding

レーザーによってチップまたはウエハを基板から剥離する工程

LDI

Laser direct image

LG

Laser groove

Lead

樹脂から露出している外部配線

LF

lead flame

半導体チップを支持・固定する役割をに担う、パッケージから露出している複数の外部接続端子

M

メタバース

自分のアバターを作成し行動することができるインターネット上の仮想空間

MCM

Multi chip module

チップを複数個搭載したモジュール

MIMO

Multiple Input and Multiple Output

送信機と受信機の双方で複数アンテナを用いる送受信技術

Mooreの法則

ムーア氏が発表した「半導体回路の集積密度は1年半~2年で2倍となる」という経験則

More Moore

スケーリングによらない、トランジスタの性能向上 (立体構造化など)

More then Moore

異種デバイスを集積して高性能化すること → SoC & SiP

N

O

oS

on Substrate

CoWをSubstrateに載せる工程

OSAT

Out Source Assembly and Test

実装工程の製造を請け負うメーカー

P

プロセスノード

一般的にトランジスタMOSFETのゲート配線の"幅"、または"間隔"を指す

PDB

Photonic debonding

PoP

Package on Package

パッケージの上にパッケージを積層させること。パッケージを重ねることでデバイス内のパッケージの占有面積を減らす。

PP

Prepreg

プリプレグ ガラス繊維、炭素繊維などからできた織物に未硬化の樹脂を含浸した成型材料。

PPA

Power, performance, and area

PPAC

Power, performance, area, and cost

プリント基板

部品を実装するための基板。部品間を接続するための配線が基板表面と基板内部に形成されている。

PWB

Printed Wired Board

部品が実装される前の配線だけされたプリント基板

PCB

Printed Circuit Board

部品が実装された後のプリント基板

Q

QFN

Quad flat non-leaded

四角形の側面に入出力用の端子が規則正しく並んでいるパッケージ(リードはなし)

QFP

Quad flat package

四角形の側面に入出力用のリードが規則正しく並んでいるパッケージ

R

RDL / 再配線層

Re-Distribution Layer

チップの入出力パッドからパッケージの入出力パッドへと信号をやりとりする高密度な配線層

S

SA D2W

Self assembly die to wafer

SoC

System on Chip

1つの半導体チップ上に異なる機能を集積する技術。例えば、CPUと大容量Memory、高耐圧電源ICと低電圧CPU、などをワンチップ化。SoCの欠点は、高い歩留まりをKeepするのが困難であることと、製造工期が長い。

SoIC

System on Integrated Chips

tsmcのチップの積層技術。Hybrid bondingを用いたCu-Cu直接接合。

SoIS

System on Integrated Substrate

InFOデバイスに対して、更にFan-Outの配線層を形成。大型デバイス用。

SQB

Sequential bonding

each die is bonded completely before the next die is placed and bonded

SSDs

Solid-state drives

フラッシュメモリーを用いるドライブ装置

SiP

System in Package

複数の半導体チップを1つのパッケージ内に封止する技術。半導体Chipをそれぞれ作製し、実装プロセスで組み合わせる。SiPの欠点は、チップ間の配線を設けるため、SoCと比較して応答速度などで性能が低いこと。

再配線層 / RDL

チップの入出力パッドからパッケージの入出力パッドへと信号をやりとりする高密度な配線層

SMT / 表面実装

Surface Mount Technology

プリント基板の表面にデバイスを実装する方法

SLIM

SiliconーLess Integrated Module

AmkorのTSV Heterogeneous integration

SLIT

SiliconーLess Interconnect technology

AmkorのTSV less Heterogeneous integration

SWIFT

Silicon Wafer Integrated Fan-Out Technologhy

AmkorのTSV less Heterogeneous integration

S-connect

AmkorのBrigdeを使用したTSV less Heterogeneous integration

S-SWIFT

Substrate SWIFT

AmkorのTSV less Heterogeneous integration。SWIFT構造を基板に実装する。

T

TB

Temporary bonding

仮固定ウエハにチップを接着する工程

TBDB

Temporary bonding and debonding

仮固定ウエハにチップを接着、剥離する工程

TCB

Thermo compression bonding

熱処理によって仮固定ウエハにチップをBondingする工程

TGV

Through Glass Via

ガラス基板に垂直に形成されたVia。

TIM

Thermal inteface material

熱伝導性材料。パッケージ内の放熱を促す。

TIV

Through InFO Via

InFO PoPに使用されている、上下のパッケージを繋ぐためのモールド樹脂を貫通するVia。

TSV

Through Silicon Via

シリコン基板に垂直に形成されたVia。

U

V

VeCS

Vertical Conductive Structures

VCB

Vertical Collective Bonding

the first dies are picked, aligned and bonded at low temperature for a very short time.Only after attaching the last die, a complete TCB profile is applied to the multilayer stack.

W

WB

Wire bonding

信号の取り出し口がBumpではなく、Wireを用いた実装方法

WLCSP

Wafer Level Chip Size Package

ウエハプロセスで再配線層からダイシングまでを実施する工程

WLP

Wafer Level Package

ウエハのまま必要な再配線や封止、Bumpの搭載などを行い、個片化するプロセス

WoS

Wafer on Substrate

WoW

Wafer on Wafer

X

XDFOI

X-Dimensional Fan-Out Integration

J-CETのTSV less WLP technology

Y

Z

2

2D実装

チップとチップを配線基板で繋ぐ実装方法。

2.xD実装

チップと樹脂基板の間に配線基板を用いる実装方法。配線基板のことをインターポーザーと呼ぶ。

2.1D実装

2.xD実装で、インタポーザーに、有機基板を使った場合の呼称

2.3D実装

2.xD実装で、インタポーザーに、微細パターニングフィルム+有機基板を使った場合の呼称

2.5D実装

2.xD実装で、インタポーザーに、Si基板を使った場合の呼称

3

3D実装

チップ同士を積層した実装方法

実装技術の動画による解説はこちら

WLPの製造工程はこちら

VCSELプロセスで必要となるドライエッチングの技術を紹介します。

VCSEL Mesa加工

VCSEL に用いられているGaAs 等のⅢ-Ⅴ族化合物半導体のエッチングには塩素系ガスが使用され,AlGaAs/GaAs 多層膜には反応性主体の条件が用いられるため,形状やウェハ面内分布の制御が難しいです。さらに,化合物半導体のエッチングでは,プロセス条件だけでは形状とウェハ面内分布制御の両立が困難です。

そこで、NE ドライエッチング装置では,アンテナ構造にISM(ICP with Static Magnetic field)方式を用いています。ISM 方式を用いたアンテナはプラズマ分布の最適化が可能であり,GaAs ウェハのエッチング面内分布で3% 以下の非常に均一な分布が得られます。実際のエピ構造による形状分布も面内で均一な形状が得られています。

メサの深さ制御については,IEP(Interferometry End Point:光干渉による終点検知)システムを用いることで,高精度にエッチングの深さを制御可能です。本システムを使用して得られた干渉波形を示すDBR 層を含め積層構造がエッチングされている様子が把握でき,この波形を監視しながらDBR ペア数をカウントすることで,任意の深さでエッチングを停止することができます。

VCSEL製造プロセスはこちら

自動運転で必要となってくるLiDAR等の3Dセンシング技術の光源として半導体レーザの市場が活発になっています。その中の一つとして大小型化、省エネなどのメリットのあるVCSEL(Vertical Cavity Surface Emitting Laser:面発光レーザー)向けのドライプロセスを紹介します。

VCSELのプロセスフロー

1. エピタキシャル成長

GaAs(砒化ガリウム)基板上に,AlGaAs/GaAs 層を数十ペア以上からなるDBR(分布反射型Distributed Bragg Reflector) 多層膜と活性層を含む積層構造としてエピ成長させます。

2. パターニング&マスク形成

エピ層をメサと呼ばれる円柱状に形成するためのマスクパターンを形成します

3. メサ加工

ドライエッチングでメサ加工を行います。

VCSEL向けドライエッチング技術の紹介

マルチチャンバ型成膜加工装置の紹介

4. 酸化狭窄&保護膜形成

活性層近傍に設計された特定のAlGaAs 層をウェット酸化により酸化狭窄します(この酸化狭窄層は電流と光の閉じ込め構造として,VCSEL の特性を左右する非常に重要な層になります)。またメサの側壁保護膜の成膜をします。

5. 電極形成

n 型,p 型それぞれの層へ電極形成を行います。

本プロセスに関するお問い合わせはこちら

https://www.ulvac.co.jp/contact/elec_inquiry/

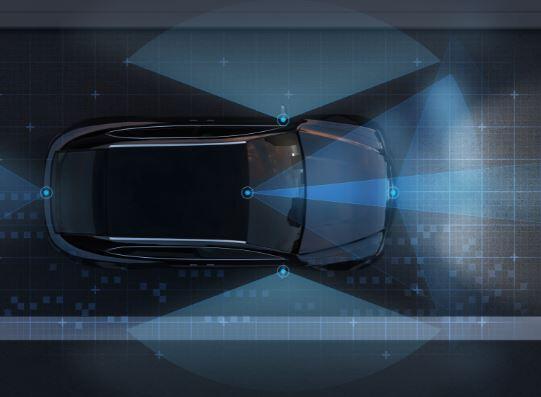

自動車産業において,電気自動車に次ぐ革命として自動運転技術の開発が進められている。自動運転を行うためには,自動車の周囲の情報を3 次元的に得る必要があり,車載用の高精度に3D センシングが可能な方法として,LiDAR(Light Detection And Ranging:光による検知と測距)がある。車載用LiDAR の市場は2018 年で15 億円程度であるが,今後自動運転技術の進歩に伴い,2024 年までには1400 億円の市場にまで達することが予測されている1)。LiDAR の原理は,レーザーをパルス状態で対象物に照射し,発光してから反射光を検出するまでの時間tを用いて,対象物との距離d を算出する(Fig.1)これはToF(Time of Flight)と呼ばれる技術であり,今後この原理を用いたセンシングデバイスはさらに増加していくものとみられる。この原理を用いたLiDAR は,①繰り返し発光するパルスレーザーと走査機構を用いた走査型LiDAR と,②高出力の単一パルスレーザーと2 次元受光素子アレイを用いたフラッシュ型LiDAR の2 種類に大きく分けられる。

現在実用化されているカメラやミリ波レーダーを用いた方式とは違い,LiDAR では赤外レーザーを用いている。Table 1 にそれぞれの特徴を一覧にした。ミリ波レーダーと比較して波長の短い赤外光を用いているため,検出の空間分解能が高く,歩行者や自転車等の検出も可能になっている。霧や雨などの悪天候時では,ミリ波レーダーと比べて検出性能が低下するが,夜間では同等の検出性能が得られる。

Table 1 Comparisons of sensors

車に搭載する特性上,デザイン面での小型化や,他のセンシングデバイスと比較して高価なため低コスト化が要求されている。そこで,赤外光源には小型な半導体レーザーが用いられている。LiDAR の普及に伴い,センシング関連の半導体レーザー市場も2018 年の180億円から,2024 年には700 億円にまで成長することが期待されている2)。

本稿では,LiDAR に用いられる半導体レーザーを紹介し,半導体レーザーの製造プロセスにおける課題と対策について,ドライプロセス技術がどのように用いられているかについて記述する。

(※この記事は、2019年9月発行のテクニカルジャーナルMo.83に掲載されたものです。)

記事の続きは下記URLよりアルバックテクニカルジャーナルに

ユーザ登録するとご覧いただけます。

https://www.ulvac.co.jp/r_d/technical_journal/tj83j/

文 献

1) P.Boulay, A.Debray, LiDAR for Automotive and Industrial Applications 2019 Report, (YoleDevelopment, 2019)2) M.Vallo, P.Mukish, Edge Emitting Lasers: Market & Technology Trends report(Yole Development, 2019)

リチウムイオン二次電池(Lithium-ion Battery : LiB)は,スマートフォン,ドローン,電気自動車(Electric Vehicle : EV)といった幅広い用途に適用され,市場規模は急速に拡大することが予想されている。特に自動車市場においては,欧州のEuro7 をはじめとする各主要国での排ガス規制の高まりや米国加州のZero Emission Vehicle(ZEV)規制強化,中国のNew Energy Vehicle( NEV)規制の動きを受け,従来の化石燃料を用いたエンジン技術ではこれらの規制をクリアすることが困難である。そのため,EV やプラグインハイブリッド車(Plug-in Hybrid Vehicle : PHV,PHEV)の普及に各自動車メーカーは舵切りを始めている1)。

シンクタンクの調査によると2040 年にはEV/ PHV の世界販売台数が6000 万台に上るという予測があり2),それに伴って電池容量の需要も急増すると言われている。従って,生産設備の増強や大容量の電池開発が急務であり,その実用化に向け各電池メーカーがしのぎを削っている。

(※この記事は、2019年9月発行のテクニカルジャーナルMo.83に掲載されたものです。)

LiB における負極

現行LiB とLi 金属負極を用いた次世代LiB

LiB は正極,負極,セパレータがFig.1 のように重ねられた状態で電解液に浸されている構造である。前述のように電池容量を向上させるために,各部材の材料や製法に関する開発が進められている。現在,負極はグラファイト塗工膜が用いられ,その理論容量密度は370mAh/g である。そのグラファイト負極を容量密度の大きい材料に変更することで,大容量化が図れる3)。

特に,3860mAh/g の理論容量密度を持つLi 金属負極に置き換えることが理想的と考えられ,次世代の負極材料の一つとして注目されている。

圧延Li 箔を用いた負極の課題

Li 金属は容量にとって理想的な系であるが,安全性と寿命の観点で課題がある。これらは,充放電反応をくり返した際に生じるデンドライトと呼ばれる針状にLi 金属が析出する問題4)が原因と考えられる。このデンドライトが成長し続けることで,正極と負極の短絡を引き起こし,発火等の原因となる。

またFig.2 に示すように,成長過程において脱落したデッドLi という充放電に寄与しないLi が生じ,電池寿命の点で課題が残されている5)。デンドライトは充電時の負極に生じる電流集中が原因と言われており6),Li 表面を平坦にし,かつ均一な表面被膜を形成することで電流分布を改善し,抑制することができると考えられる。現在,Li 金属負極として一般的に用いられる圧延プロセスにより作製したLi 箔は,圧延ローラーの表面粗度,プロセス雰囲気といった観点から前述の課題を解決できていないと考えられる。筆者らはこれらの課題を解決する手法として,表面平滑性に優れ,雰囲気制御ができる真空蒸着プロセスに着目した。さらに,現行の量産塗工ラインに適用することも視野に入れ,巻取蒸着法を選択し,Li 金属負極の量産化に向け開発を行っている。

記事の続きは下記URLよりアルバックテクニカルジャーナルに

ユーザ登録するとご覧いただけます。

https://www.ulvac.co.jp/r_d/technical_journal/tj83j/

文 献

1) みずほ銀行産業調査部 : Mizuho Industry Focus 205, 11(2018).2) 国立研究開発法人 新エネルギー・産業技術総合開発機構 : focus NEDO 69, 9(2018).3) 国立研究開発法人 新エネルギー・産業技術総合開発機構 : NEDO 二次電池技術開発ロードマップ 2013(Battery RM2013), 10(2013)4) 電気化学会 電池技術委員会編, "電池ハンドブック(" オーム社, 2010)p.58.5) Xin-Bing Cheng, Rui Zhang, Chen-Zi Zhao, and Qiang Zhang : Chemical Reviews, 117, 10406(2017).6) Kiyoshi Kanamura, Naohiro Kobori, and Hirokazu Munakata : BLIX, Symposium on Energy Storage, San Jose(2017), p.6