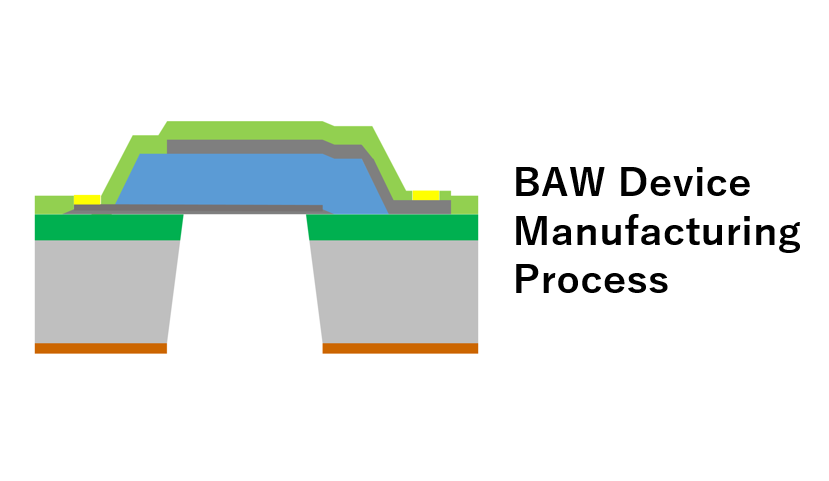

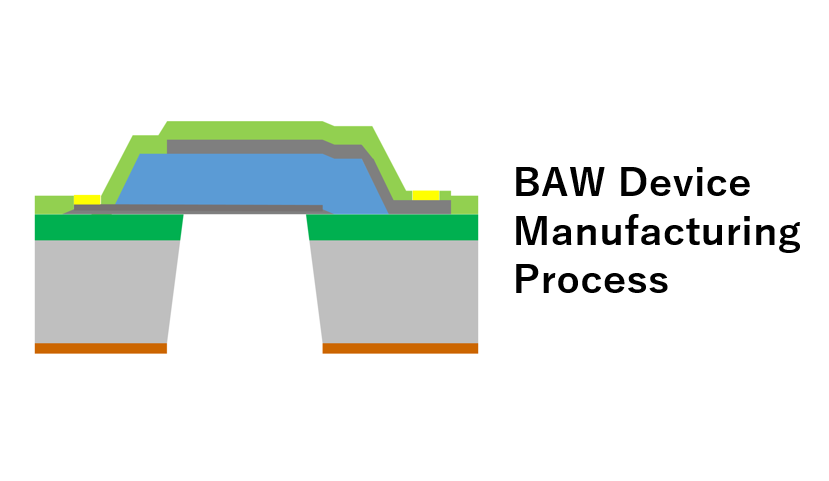

BAWデバイスとは圧電体のバルクの振動を利用して特定の周波数帯の電気信号を取り出すフィルタです。

BAWデバイスとは圧電体のバルクの振動を利用して特定の周波数帯の電気信号を取り出すフィルタです。

BAWデバイス制作に向けて必要となる圧電膜の加工技術および電極形成で活用されるULVACの技術を紹介します。 … BAWデバイス向け成膜/加工技術

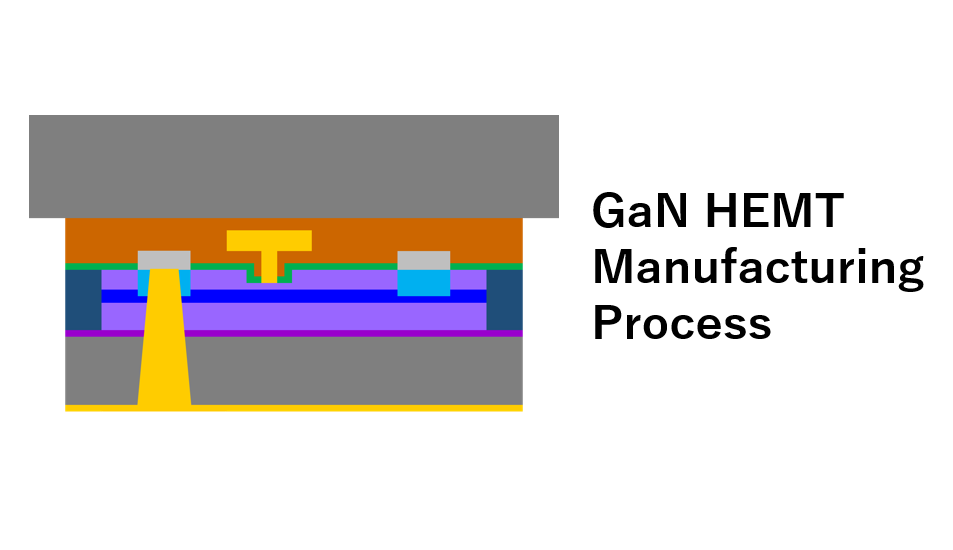

SiNだけを取り除くために低ダメージエッチングが重要となります。終点検知を行いエッチング速度を保ちながらSiNのエッチングを行うことが可能です。 … GaN HEMT構造向け成膜/加工技術

GaN HEMT(高電子移動度 トランジスタ:High Electron Mobility Transistor)は低い動作抵抗と高い破壊耐圧を有しており、高出力かつ高速の電子デバイスへの応用が期待される次世代のパワー 半導体である。 … GaN HEMTの製造プロセス

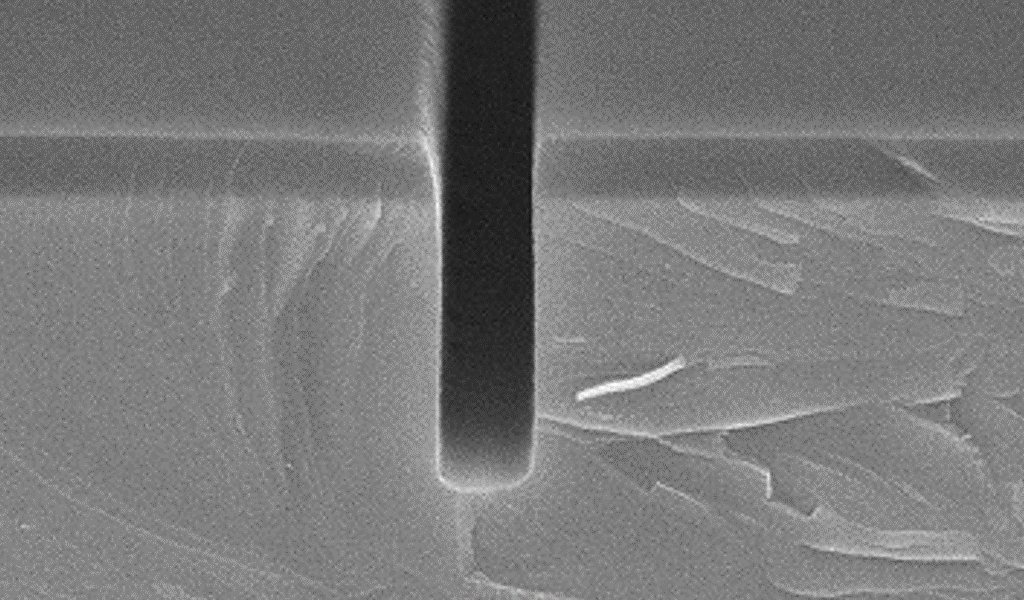

GaN HEMTにおけるゲート構造のパターンはいくつかありますが、何れにも言えることは非常に浅い加工が要求されます。

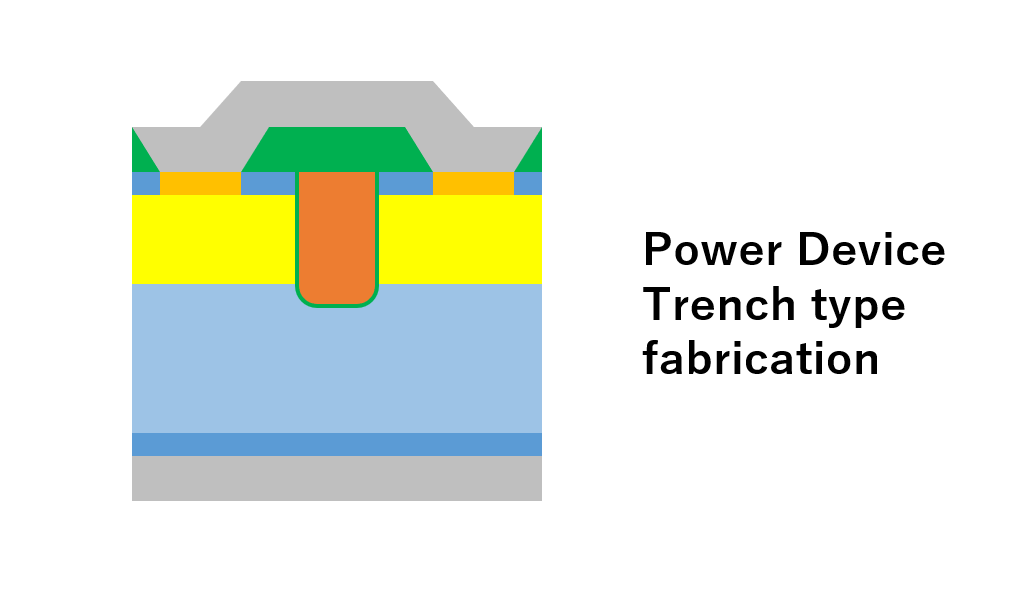

パワーデバイスは低消費電力化を実現するデバイスとして期待されています。これまでのパワーデバイスはSi基板を用いていましたが、物性限界があるため、次世代の基板としてSiCやGaNなどのワイドバンドギャップ半導体の活用が広がっています。 … トレンチ構造パワーデバイス製造プロセス

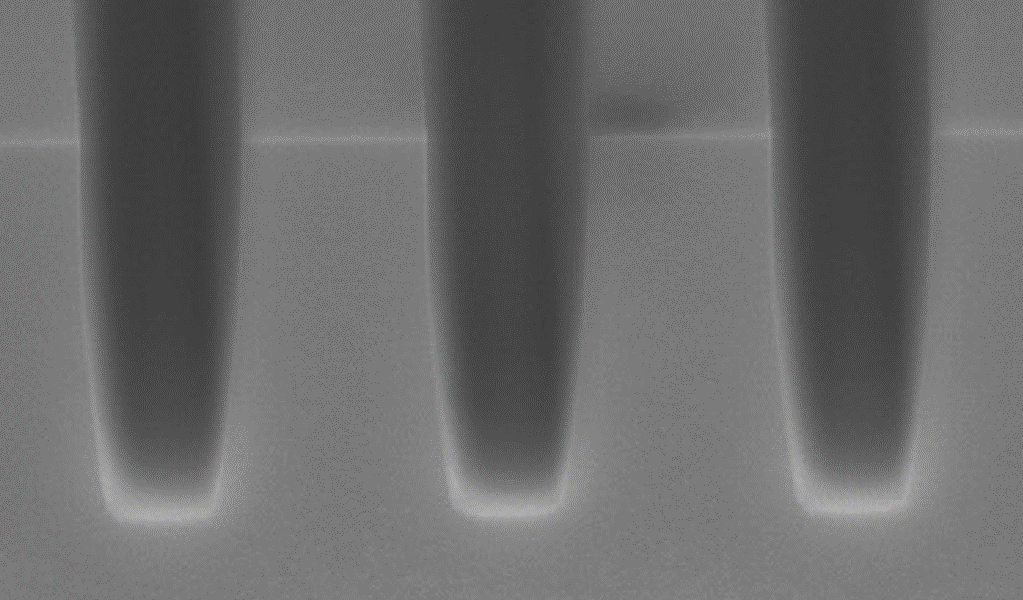

パワーデバイスの微細化、低抵抗化を実現するトレンチ構造を実現するためのドライエッチング技術を提供しています。 … GaNトレンチエッチング

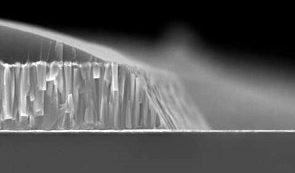

パワーデバイスの微細化、低抵抗化を実現するトレンチ構造を実現するためのドライエッチング技術を提供しています。 … SiCトレンチエッチング

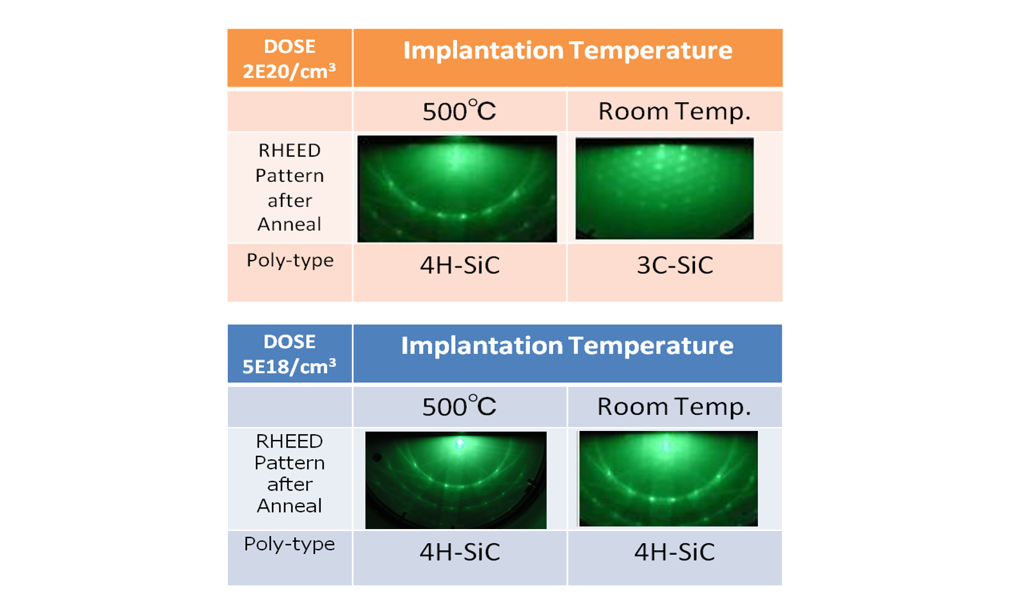

高エネルギーでの注入や、高温と低温注入の使い分けが可能なプロセスを提供します。また活性化アニールの際のSi蒸発による基板荒れを防ぐカーボンキャップ技術も提供可能です。

下部電極であるPtとの高い選択性を持つPt/PZTエッチングプロセスを提供します。(選択比例:PZT/Pt>5@8inch, >10@6inch)

また下地の掘れ量を最小化する高均一性(<+/-3%@8inch)と精密な終点検出を提供します。